402 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

11.4.6.4 Intel XScale

®

Core Events Target ID(000100) /

Design Block #(0111)

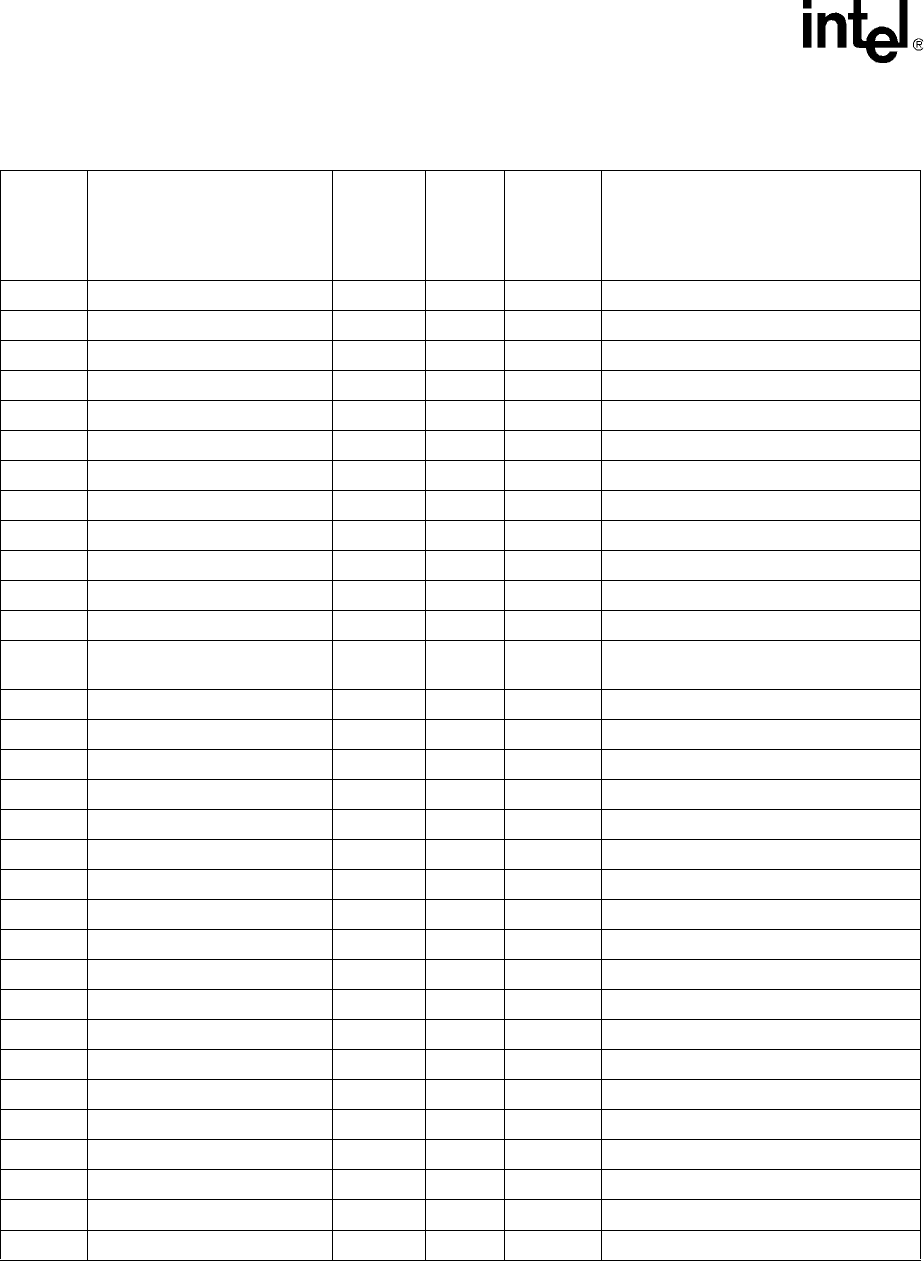

Table 158. Intel XScale

®

Core Gasket PMU Event List (Sheet 1 of 4)

Event

Number

Event Name

Clock

Domain

Single

pulse/

Long

pulse

Burst Description

0 XG_CFIFO_WR_EVEN_XS P_CLK single separate XG command FIFO even enqueue

1reserved

2 XG_DFIFO_WR_EVEN_XS P_CLK single separate XG DRAM data FIFO even enqueue

3reserved

4 XG_SFIFO_WR_EVEN_XS P_CLK single separate XG SRAM data FIFO even enqueue

5reserved

6 XG_LCFIFO_WR_EVEN_XS P_CLK single separate XG lcsr command FIFO even enqueue

7 XG_LCFIFO_WR_ODD_XS P_CLK single separate XG lcsr command FIFO odd enqueue

8 XG_LDFIFO_WR_EVEN_XS P_CLK single separate XG lcsr data FIFO even enqueue

9 XG_LDFIFO_WR_ODD_XS P_CLK single separate XG lcsr data FIFO odd enqueue

10 XG_LCSR_RD_EVEN_XS P_CLK single separate XG lcsr return data FIFO even dequeue

11 XG_LCSR_RD_ODD_XS P_CLK single separate XG lcsr return data FIFO odd dequeue

12 XG_LCSR_RD_OR_XS P_CLK single separate XG lcsr return data FIFO even_or_odd

dequeue

13 XG_PUFF0_RD_EVEN_XS P_CLK single separate XG push fifo0 even dequeue

14 XG_PUFF0_RD_ODD_XS P_CLK single separate XG push fifo0 odd dequeue

15 XG_PUFF0_RD_OR_XS P_CLK single separate XG push fifo0 even_or_odd dequeue

16 XG_PUFF1_RD_EVEN_XS P_CLK single separate XG push fifo1 even dequeue

17 XG_PUFF1_RD_ODD_XS P_CLK single separate XG push fifo1 odd dequeue

18 XG_PUFF1_RD_OR_XS P_CLK single separate XG push fifo1 even_or_odd dequeue

19 XG_PUFF2_RD_EVEN_XS P_CLK single separate XG push fifo2 even dequeue

20 XG_PUFF2_RD_ODD_XS P_CLK single separate XG push fifo2 odd dequeue

21 XG_PUFF2_RD_OR_XS P_CLK single separate XG push fifo2 even_or_odd dequeue

22 XG_PUFF3_RD_EVEN_XS P_CLK single separate XG push fifo3 even dequeue

23 XG_PUFF3_RD_ODD_XS P_CLK single separate XG push fifo3 odd dequeue

24 XG_PUFF3_RD_OR_XS P_CLK single separate XG push fifo3 even_or_odd dequeue

25 XG_PUFF4_RD_EVEN_XS P_CLK single separate XG push fifo4 even dequeue

26 XG_PUFF4_RD_ODD_XS P_CLK single separate XG push fifo4 odd dequeue

27 XG_PUFF4_RD_OR_XS P_CLK single separate XG push fifo4 even_or_odd dequeue

28 XG_SYNC_ST_XS P_CLK single separate XG in sync. state

29 reserved

30 reserved

31 reserved