426 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

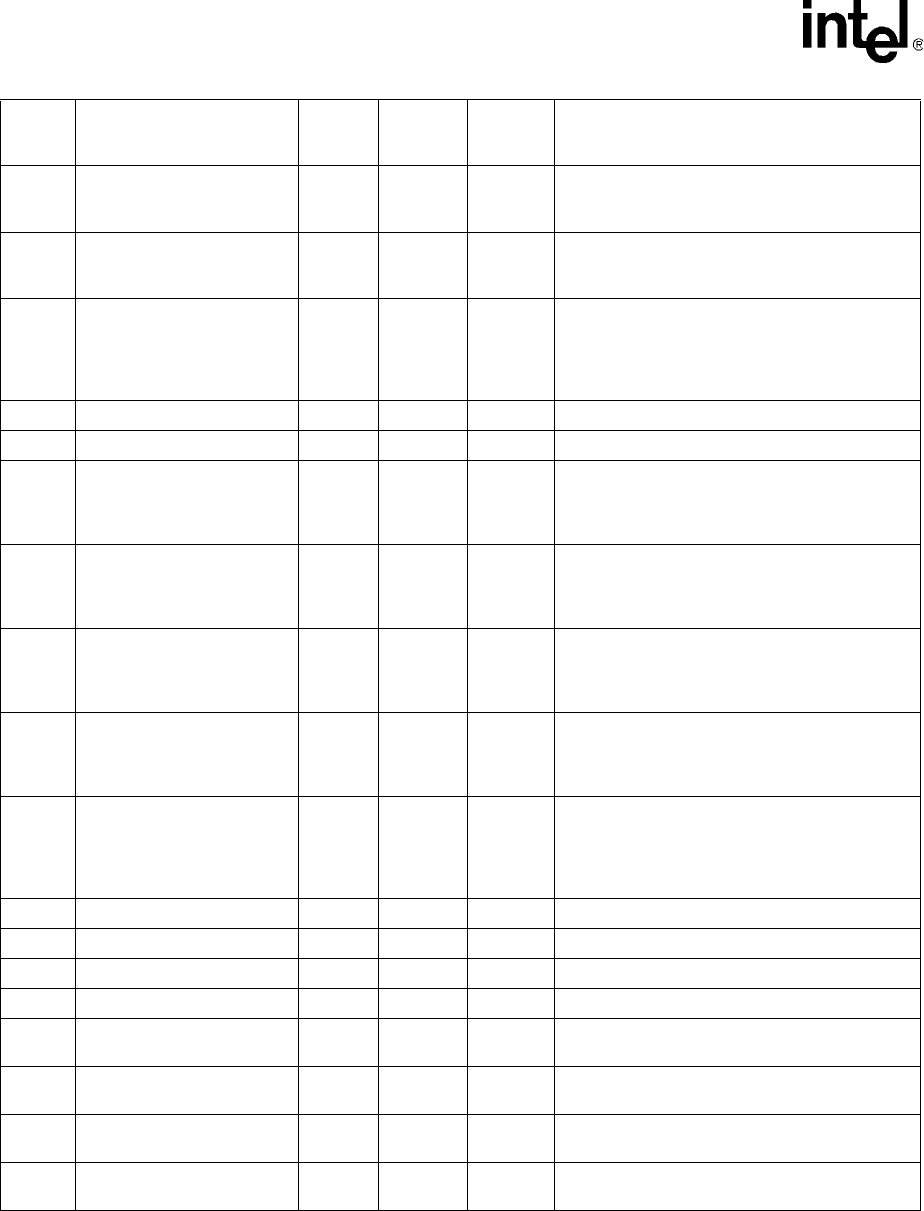

14 deq_push_ctrl_wph P_CLK single separate

Active when dequeueing from the push control

FIFO; occurs on the last cycle of a burst or on the

only cycle of a single transfer.

15

d_push_ctrl_fsm/

single_xfer_wph

P_CLK single separate

Active if the data is about to be transferred from

d_push data FIFO to the dp_unit FIFO is length 0,

i.e., a single 8-byte transfer.

16

d_push_ctrl_fsm/

data_128_bit_alligned

P_CLK single separate

Active if the data is about to be transferred from

d_push data FIFO to the dp_unit FIFO is quad-

word (128-bit) aligned.

17 perf_data_fifo_full P_CLK single separate

Asserts when the data FIFO in the d_push_bus_if

block has > 4 entries (Data from the RDRAM is

enqueued into this FIFO; dequeued data is

written to the push bus arbiter FIFO in dp_unit

block.)

18 reserved

19 reserved

20

DPL_RMW_BANK3_READ_

DATA_AVAIL_RPH

P_CLK single separate

Indicates that the read data for a read-modify-

write operation is available in the d_pull_bus_if

block. This signal is deasserted when the data

and command

21

DPL_RMW_BANK2_READ_

DATA_AVAIL_RPH

P_CLK single separate

Indicates that the read data for a read-modify-

write operation is available in the d_pull_bus_if

block. This signal is deasserted when the data

and command

22

DPL_RMW_BANK1_READ_

DATA_AVAIL_RPH

P_CLK single separate

Indicates that the read data for a read-modify-

write operation is available in the d_pull_bus_if

block. This signal is deasserted when the data

and command

23

DPL_RMW_BANK0_READ_

DATA_AVAIL_RPH

P_CLK single separate

Indicates that the read data for a read-modify-

write operation is available in the d_pull_bus_if

block. This signal is deasserted when the data

and command

24 addr_128bit_alligned P_CLK single separate

Indicates that bit 3 of the DRAM command’s

address at the head of the pull control FIFO (i.e.,

about to be dequeued) is low. This command is

for the pull data which is about to be enqueued

into a pull data bank FIFO.

25 b3_empty_rph P_CLK single separate Indicates that the pull data’s bank FIFO is empty.

26 b2_empty_rph P_CLK single separate Indicates that the pull data's bank FIFO is empty.

27 b1_empty_rph P_CLK single separate Indicates that the pull data's bank FIFO is empty.

28 b0_empty_rph P_CLK single separate indicates that the pull data's bank FIFO is empty

29 b3_full_rph P_CLK single separate

Indicates that the pull data's bank FIFO has > 0xf

entries in it, i.e., is full

30 b2_full_rph P_CLK single separate

Indicates that the pull data's bank FIFO has > 0xf

entries in it, i.e., is full.

31 b1_full_rph P_CLK single separate

Indicates that the pull data's bank FIFO has > 0xf

entries in it, i.e., is full.

32 b0_full_rph P_CLK single separate

Indicates that the pull data's bank FIFO has > 0xf

entries in it, i.e., is full.

Table 184. IXP2800 Network Processor Dram CH2 PMU Event List (Sheet 2 of 5)