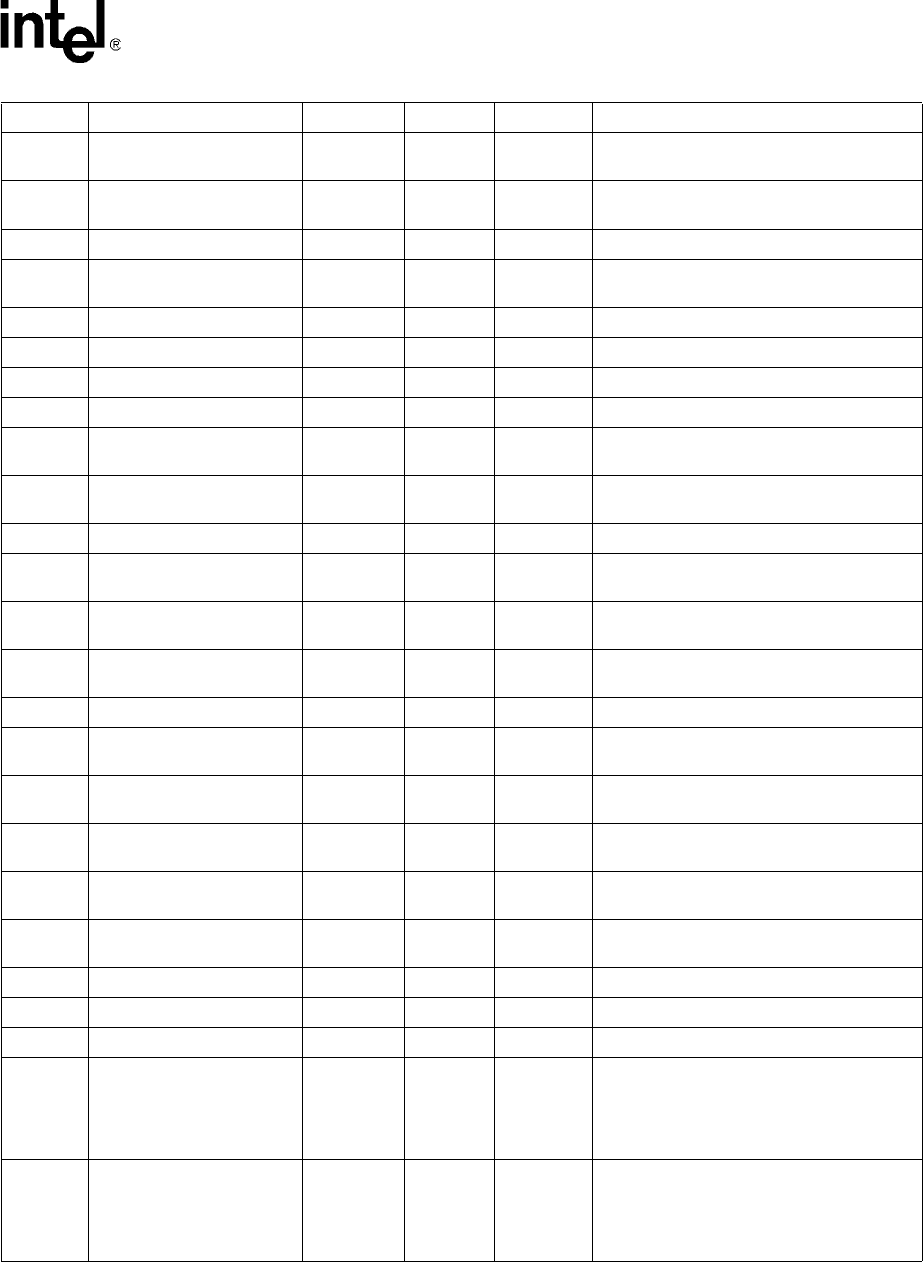

Hardware Reference Manual 397

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

19 reserved

20

S_PULL data FIFO 1

enqueue

P_CLK pulse separate

21

S_PULL data FIFO 1

dequeue

P_CLK pulse separate

22 S_PULL data FIFO 1 full P_CLK level separate

23

S_PULL data FIFO 1 not

empty

P_CLK level separate

24 Tbuffer Partition 0 full P_CLK level separate Indicates partition 0 of the tbuffer is full

25 Tbuffer Partition 1 full P_CLK level separate Indicates partition 1 of the tbuffer is full

26 Tbuffer Partition 2 full P_CLK level separate Indicates partition 2of the tbuffer is full

27 reserved

28

Rx_Thread_Freelist 0

enqueue

P_CLK pulse separate

29

Rx_Thread_Freelist 0

dequeue

P_CLK pulse separate

30 Rx_Thread_Freelist 0 full P_CLK level separate

31

Rx_Thread_Freelist 0 not

empty

P_CLK level separate

32

Rx_Thread_Freelist 1

enqueue

P_CLK pulse separate

33

Rx_Thread_Freelist 1

dequeue

P_CLK pulse separate

34 Rx_Thread_Freelist 1 full P_CLK level separate

35

Rx_Thread_Freelist 1 not

empty

P_CLK level separate

36

Rx_Thread_Freelist 2

enqueue

P_CLK pulse separate

37

Rx_Thread_Freelist 2

dequeue

P_CLK pulse separate

38

Rx_Thread_Freelist 2

empty

P_CLK level separate

39

Rx_Thread_Freelist 2 not

full

P_CLK level separate

40 reserved

41 reserved l

42 reserved

43 Detect No Calendar MTS_CLK level separate

Indicates that a framing pattern has been

received on the TSTAT inputs for greater

than 32 clock cycles; the valid signal from

the MTS_CLK domain is synchronized; as

such, it yields an approximate value.

44 Detect FC_IDLE MRX_CLK level separate

Indicates that an idle cycle has been

received on the RXCDAT inputs for greater

than 2 clock cycles; the valid signal from the

MTS_CLK domain is synchronized; as such,

it yields an approximate value.

Table 157. IXP2800 Network Processor MSF PMU Event List (Sheet 2 of 6)