Hardware Reference Manual 357

Intel

®

IXP2800 Network Processor

PCI Unit

The BE_BEMI bit of the PCI_CONTROL register can be set to enable big-endian on the incoming

byte enable from the PCI Bus to both the SRAM and DRAM. The BE_BEMO bit of the

PCI_CONTROL register can be set to enable big-endian on the outgoing byte enable to the PCI

Bus from both the SRAM and DRAM.

The B-stepping silicon provides a mechanism to enable byte swapping for PCI I/O operations as

described in Table 146.

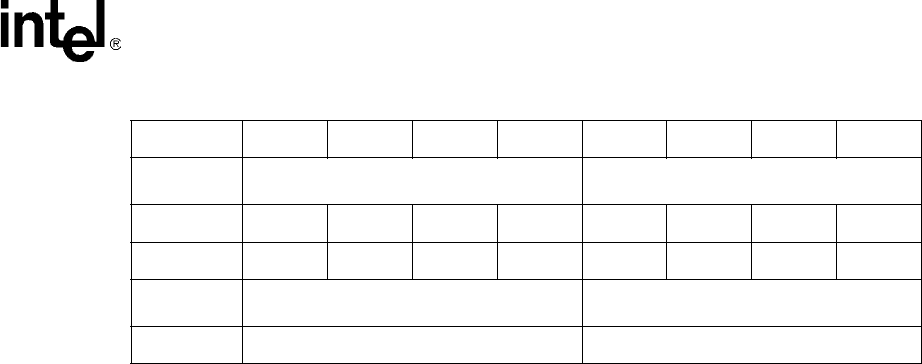

Table 145. Byte Enable Alignment for 32-Bit PCI Data Out (Big-Endian to 32 Bits PCI Big

Endian without Swap)

SRAM Data

IN_BE[0] IN_BE[1] IN_BE[2] IN_BE[3] IN_BE[0] IN_BE[1] IN_BE[2] IN_BE[3]

Longword1byte enable

LW1 byte enable drive after LW0 byte enable

Longword0 byte enable

LW0 byte enable drive first

DRAM Data

IN_BE[4] IN_BE[5] IN_BE[6] IN_BE[7] IN_BE[0] IN_BE[1] IN_BE[2] IN_BE[3]

PCI Data

OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3] OUT_BE[0] OUT_BE[1] OUT_BE[2] OUT_BE[3]

Longword1byte enable

LW1 byte enable drive after LW0 byte enable

Longword0 byte enable

LW0 byte enable drive first

PCI Add[2]=1 PCI Add[2]=0