Hardware Reference Manual 53

Intel

®

IXP2800 Network Processor

Technical Description

Each channel can be expanded by depth according to the number of port enables available. If

external decoding is used, then the number of SRAMs used is not limited by the number of port

enables generated by the SRAM controller.

Note: Doing external decoding may require external pipeline registers to account for the decode time,

depending on the desired frequency.

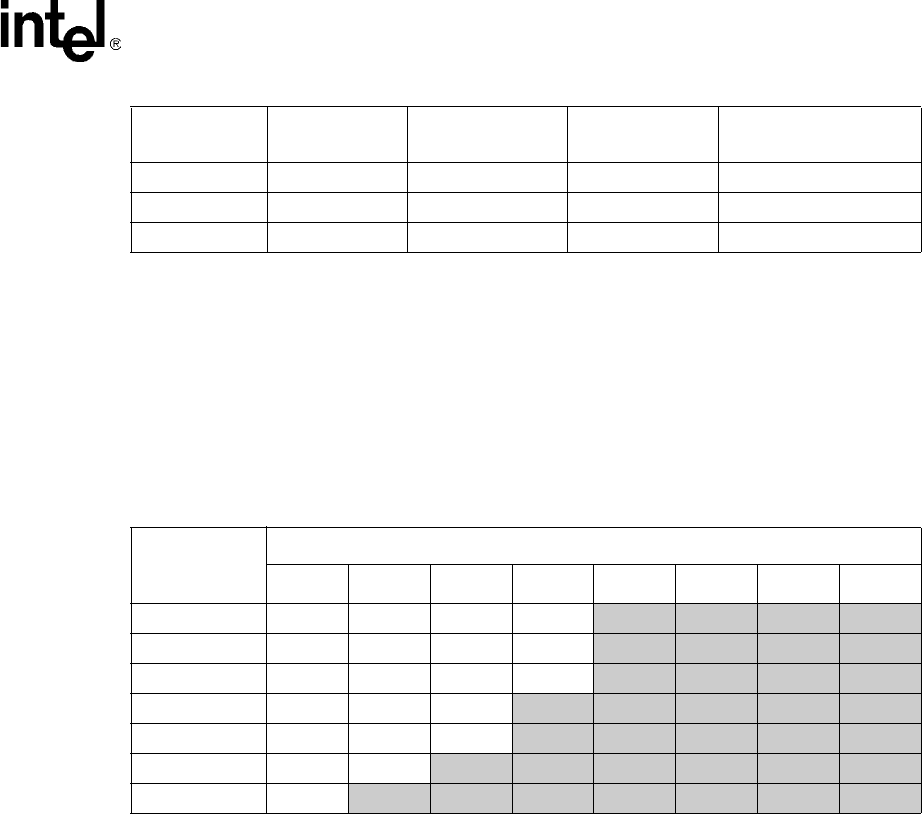

Maximum SRAM system sizes are shown in Table 11. Shaded entries require external decoding,

because they use more port enables than the SRAM controller can supply directly.

2.5.3 SRAM Atomic Operations

In addition to normal reads and writes, SRAM supports the following atomic operations.

Microengines have specific instructions to do each atomic operation; Intel XScale

®

microarchitecture uses aliased address regions to do atomic operations.

• bit set

• bit clear

• increment

• decrement

• add

• swap

The SRAM does read-modify-writes for the atomic operations, the pre-modified data can also be

returned if desired. The atomic operations operate on a single 32-bit word.

8M x 18 16 MB 21:0 23:22 3

16M x 18 32 MB 22:0 None 2

32M x 18 64 MB 23:0 None 2

Table 10. SRAM Controller Configurations (Sheet 2 of 2)

SRAM

Configuration

SRAM Size

Addresses Needed

to Index SRAM

Addresses Used

as Port Enables

Total Number of Port

Select Pairs Available

Table 11. Total Memory per Channel

SRAM Size

Number of SRAMs on Channel

12345678

512K x 18 1 MB 2 MB 3 MB

4 MB 5 MB 6 MB 7 MB 8 MB

1M x 18 2 MB 4 MB 6 MB 8 MB 10 MB 12 MB 14 MB 16 MB

2M x 18 4 MB 8 MB 12 MB 16 MB 20 MB 24 MB 28 MB 32 MB

4M x 18 8 MB 16 MB 24 MB 32 MB 64 MB NA NA NA

8M x 18 16 MB 32 MB 48 MB 64 MB NA NA NA NA

16M x 18 32 MB 64 MB NA NA NA NA NA NA

32M x 18 64 MB NA NA NA NA NA NA NA