138 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.12.3 UART Operation

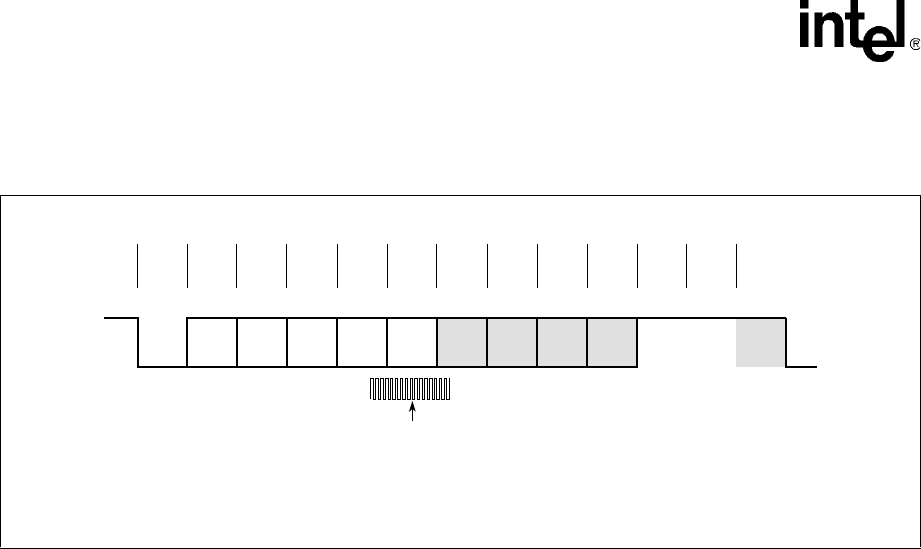

The format of a UART data frame is shown in Figure 31.

Figure 31. UART Data Frame

Each data frame is between 7 bits and 12 bits long depending on the size of data programmed, if

parity is enabled and if two stop bits is selected. The frame begins with a start bit that is represented

by a high to low transition. Next, either 5 to 8 bits of data are transmitted, beginning with the least

significant bit. An optional parity bit follows, which is set if even parity is enabled and an odd

number of ones exist within the data byte, or if odd parity is enabled and the data byte contains an

even number of ones. The data frame ends with one, one and a half, or two stop bits as programmed

by the user, which is represented by one or two successive bit periods of a logic one.

3.12.3.1 UART FIFO OPERATION

The UART has one transmit FIFO and one receive FIFO. The transmit FIFO is 64 bytes deep and

eight bits wide. The receive FIFO is 64 bytes deep and 11 bits wide.

3.12.3.1.1 UART FIFO Interrupt Mode Operation –

Receiver Interrupt

When the Receive FIFO and receiver interrupts are enabled (UART_FCR[0]=1 and

UART_IER[0]=1), receiver interrupts occur as follows:

• The receive data available interrupt is invoked when the FIFO has reached its programmed

trigger level. The interrupt is cleared when the FIFO drops below the programmed trigger

level.

• The UART_IIR receive data available indication also occurs when the FIFO trigger level is

reached, and like the interrupt, the bits are cleared when the FIFO drops below the trigger

level.

• The receiver line status interrupt (UART_IIR = C6H), as before, has the highest priority. The

receiver data available interrupt (UART_IIR=C4H) is lower. The line status interrupt occurs

only when the character at the top of the FIFO has errors.

• The data ready bit (DR in UART_LSR register) is set to 1 as soon as a character is transferred

from the shift register to the Receive FIFO. This bit is reset to 0 when the FIFO is empty.

B1741-02

Start

Bit

Data

<0>

Data

<1>

Data

<2>

Data

<3>

Data

<4>

Data

<5>

Data

<6>

Data

<7>

Parity

Bit

Stop

Bit 1

Stop

Bit 2

TXD or RXD pin

Notes:

Receive data sample counter frequency = 16x bit frequency, each bit is sampled three times in the middle.

Shaded bits are optional and can be proammed by users.

MSBLSB