282 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

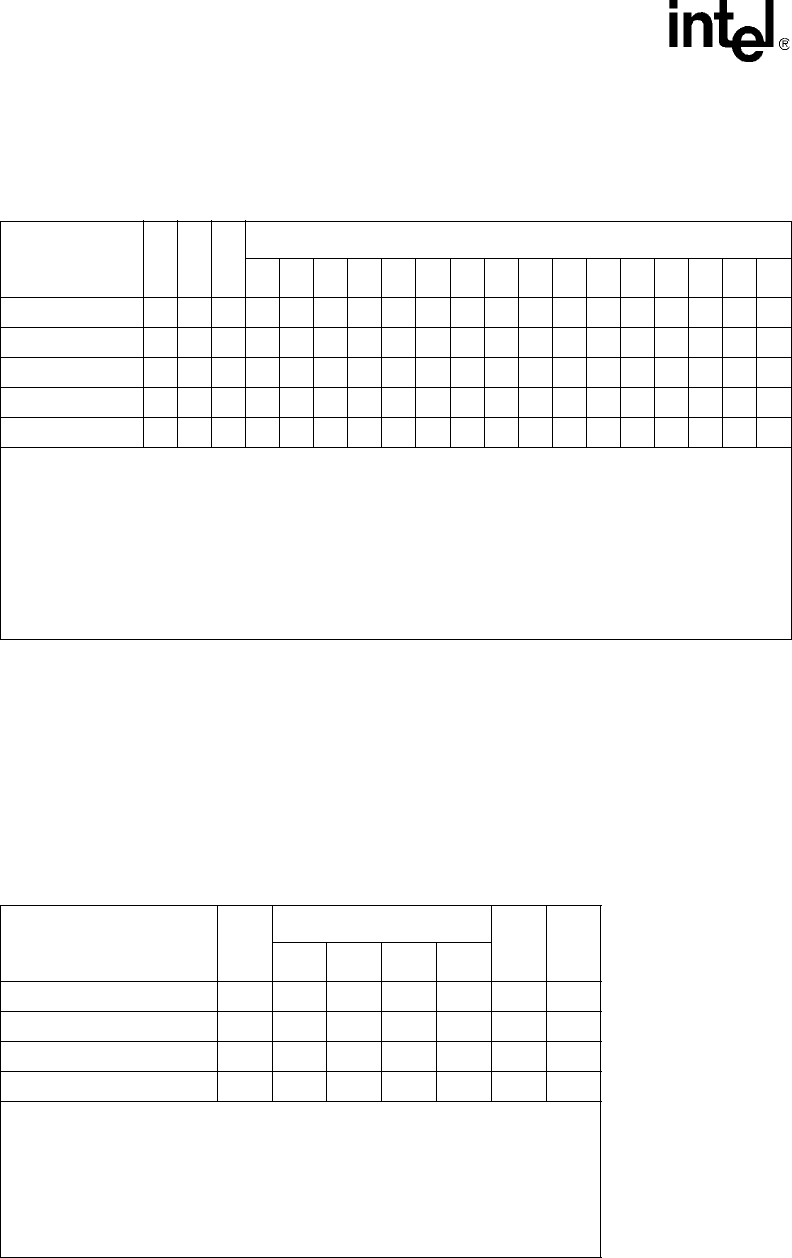

8.6.1 Data Training Pattern

The data pin training sequence is shown in Table 107. This is a superset of SPI-4 training sequence,

because it includes the TPAR/RPAR and TPROT/RPOT pins, which are not included in SPI-4.

8.6.2 Flow Control Training Pattern

This section defines training for the flow control pins (Table 108). These pins are normally used for

CSIX flow control (Section 8.5), but can be programmed for use as SPI-4 Status Channel. The

training pattern used is based on the usage.

The flow control pin training sequence when the pins are used for CSIX flow control is shown in

Table 108.

Table 107. Data Training Sequence

Cycle

(Note 4)

PROT

PAR

CTL

DATA

1514131211109876543210

1 (Note 5) 0x10xx000000000abcd

2 to 11 0110000111111111111

12 to 21 1001111000000000000

20α-18 to 20α-90110000111111111111

20α-8 to 20α+1 1001111000000000000

NOTES:

1. In cycle 1, x and abcd depend on the contents of the interval after the last preceding control word. This is

an Idle Control Word.

2. α represents the number of repeats, as specified in SPI-4 specification. When the IXP2800 Network

Processor is transmitting training sequences the value is in Train_Data[Alpha].

3. On receive, the IXP2800 Network Processor will do dynamic deskew when Train_Data[Ignore_Training]

is 0, and RCTL = 1 and RDATA = 0x0FFF for three consecutive samples. Note that RPROT and RPAR are

ignored when recognizing the start of training sequence.

4. These are really phases (i.e.,each edge of the clock is counted as one sample).

5. This cycle is valid for SPI-4, it is not used in CSIX training.

Table 108. Flow Control Training Sequence

Cycle

(Note 3)

XCSOF

XCDAT

XCPAR

XCSRB

3210

1 to 10 1110000

11 to 20 0001111

20α-19 to 20α-10 1110000

20α-9 to 20α 0001111

NOTE:

1. α represents the number of repeats, as specified in SPI-4 specification. When

the IXP2800 Network Processor is transmitting training sequences the value is

in Train_Flow_Control[Alpha].

2. On receive, the IXP2800 Network Processor will do dynamic deskew when

Train_Flow_Control[Ignore_Training] is 0, and RXCSOF = 1, RXCDATA =

0xC, RXCPAR =0, and RXCSRB = 0 for three consecutive samples.

3. These are really phases (i.e.,each edge of the clock is counted as one sample).