Hardware Reference Manual 211

Intel

®

IXP2800 Network Processor

SRAM Interface

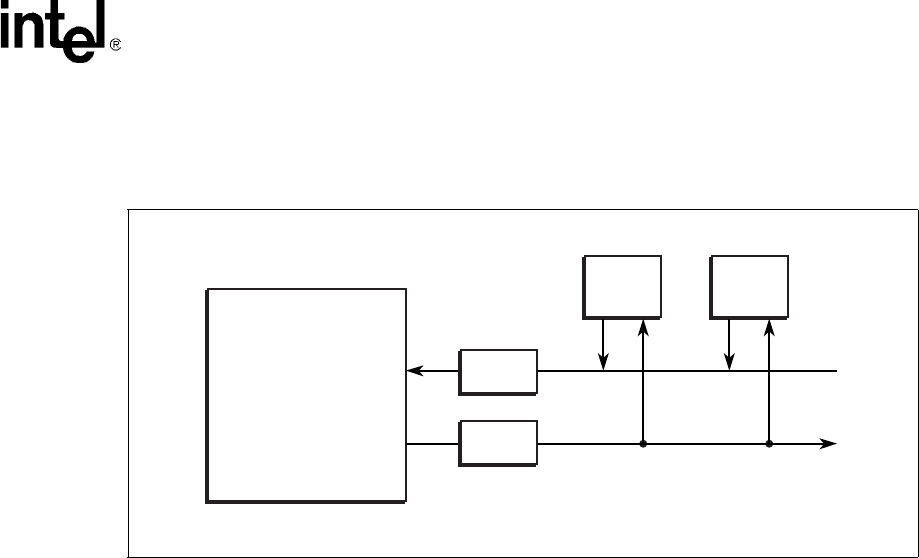

A side-effect of the pipeline registers is to add latency to reads, and the SRAM controller must

account for that delay by waiting extra cycles (relative to no external pipeline registers) before it

registers the read data. The number of extra pipeline delays is programmed in

SRAM_Control[Pipeline].

6.4 Command Overview

This section will give an overview of the SRAM commands and their operation. The details will be

given later in the document. Memory reference ordering will be specified along with the detailed

command operation.

6.4.1 Basic Read/Write Commands

The basic read and write commands will transfer from 1 – 16 longwords of data to or from the

QDR SRAM external to the IXP2800 Network Processor.

For a read command, the SRAM is read and the data placed on the Push bus, one longword at a

time. The command source (for example, the Microengine) is signaled that the command is

complete during the last data phase of the push bus transfer.

For a write command, the data is first pulled from the source, then written to the SRAM in

consecutive SRAM cycles. The command source is signaled that the command is complete during

the last data phase of the pull bus transfer.

If a read operation stalls due to the pull-data FIFO filling, any concurrent write operation that is in

progress to the same address is temporarily stopped. This technique results in atomic data reads.

6.4.2 Atomic Operations

The SRAM Controller does read-modify-writes for the atomic operations, and the pre-modified

data can be returned if desired. Other (non-atomic) readers and writers can access the addressed

location between the read and write portions of the read-modify-write. Table 72 describes the

atomic operations supported by the SRAM Controller.

Figure 76. External Pipeline Registers Block Diagram

A9735-01

Q

Addr, BWE, etc.

SRAM SRAM

Intel

®

IXP2800

Network

Processor

Register

Register