Hardware Reference Manual 379

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

11.1.5 Definition of CHAP Terminology

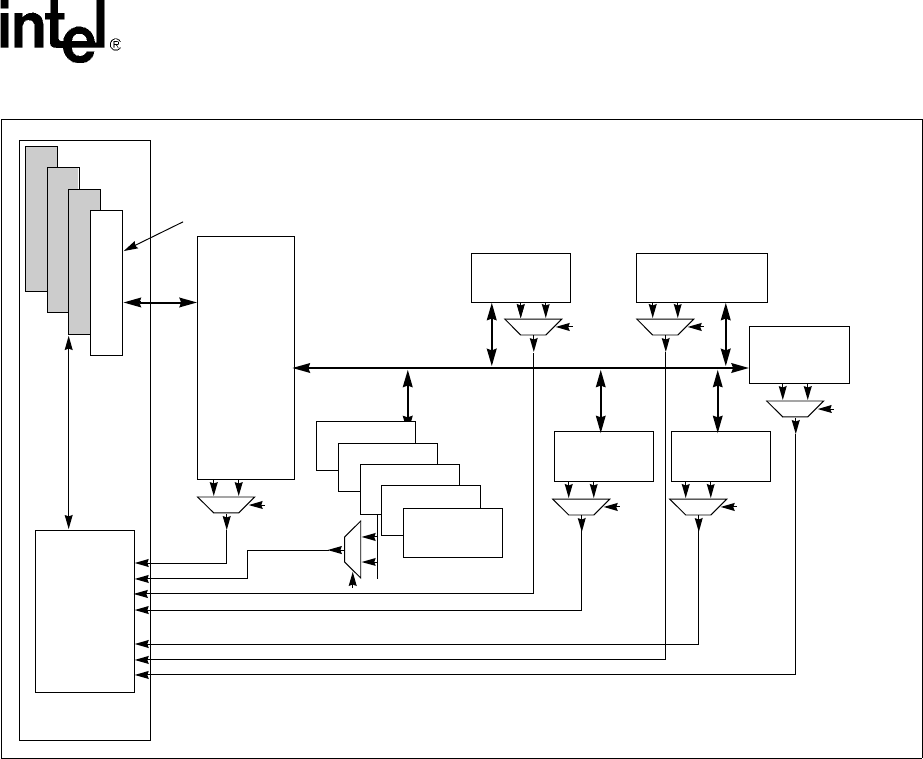

Figure 138. Basic Block Diagram of IXP2800 Network Processor with PMU

Duration Count

The counter is incremented for each clock for which the event signal is asserted as

logic high.

MMR Memory Mapped register.

OA

Observation Architecture. The predecessor to CHAP counters that facilitates the

counting of hardware events.

Occurrence Count The counter is incremented each time a rising edge of the event signal is detected.

Preconditioning

Altering a design block signal that represents an event such that it can be counted by

the CHAP unit. The most common preconditioning is likely to be a ‘one-shot’ to count

occurrences.

RO (register) Read Only. If a register is read-only, writes to this register have no effect.

R/W (register) Read/Write. A register with this attribute can be read and written.

WO (register)

Write Once. Once written, a register with this attribute becomes Read Only. This

register can only be cleared by a Reset.

WC (register)

Write Clear. A register bit with this attribute can be read and written. However, a write

of 1 clears (sets to 0) the corresponding bit and a write of 0 has no effect.

MEDIA

I/F

PCI

I/F

Intel

XScale

®

Core

DDRAM

Control

QDR

Control

MUX Control

from PMU

Push-pull Bus

SHaC

APB Bus

Config Registers

ME1

ME2

ME3

ME4

ME8

Hardware Events

CHAP

Counters

PMU