160 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

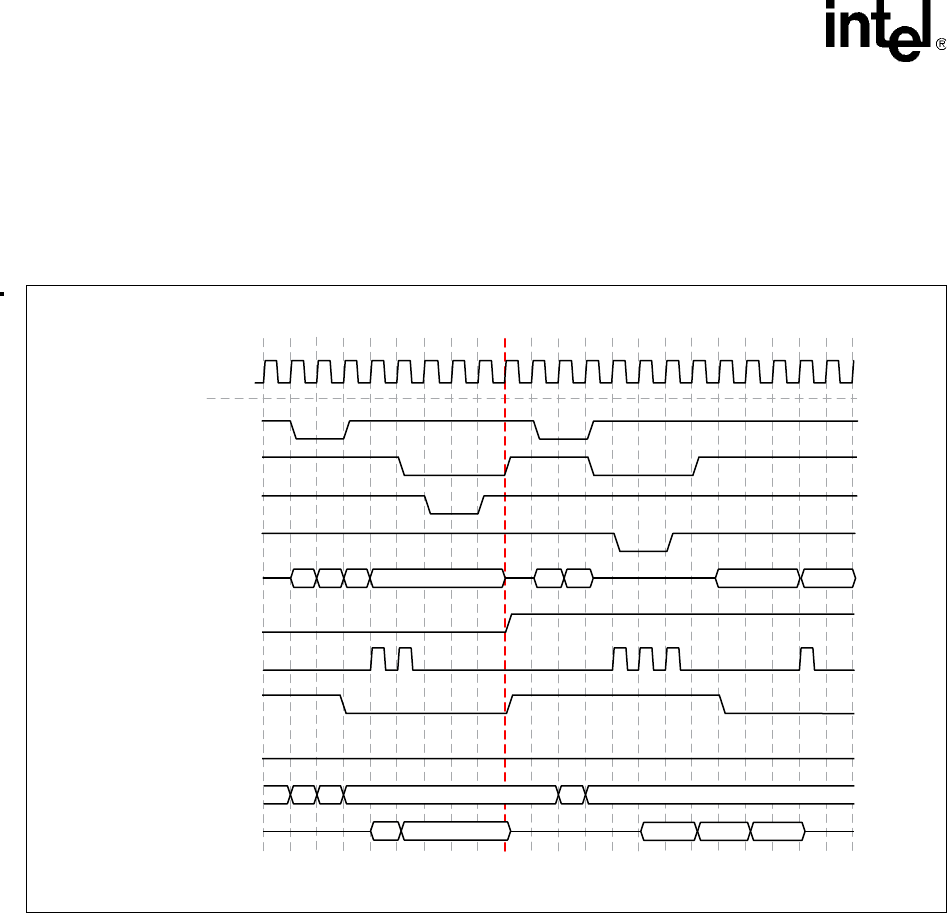

Mode 3 Write Interface Protocol

Figure 50 depicts a single write transaction launched from the IXP2800 Network Processor to the

Intel and AMCC* SONET/SDH device, followed by two consecutive reads.

Compared with the Lucent* TDAT042G5, this device has a shorter access time, about eight clock

cycles (i.e., 160 ns). In this case, an intervening cycle may not be needed for the write transactions.

Therefore, the throughput is about 12.5 Mbytes per second.

Figure 50. Mode 3 Single Write Transfer Followed by Read (B0)

B1749-04

SP_CLK

SP_ALE_L

SP_CS_L[1]/CSB

SP_WR_L/WRB

SP_RD_L/RDB

20 4 6 8 10 12 14 16 18 20

SP_AD[7:0]

SP_ACK_L/INT

SP_CP

SP_OE_L

A[10:1] A[10:1]

SP_DIR

ADDR[15:0]

DATA[15:0]

A

[10:8]

A

[7:0]

A

[15:8]

A

[7:0]

A

[15:8]

D

[15:8]

A

[7:0]

A

[7:0]

D

[7:0]

D[15:8] D[7:0]

D[15:0]

D

[15:8]

D[15:0] 2xD[15:8]D[15:0]