184 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Microengines

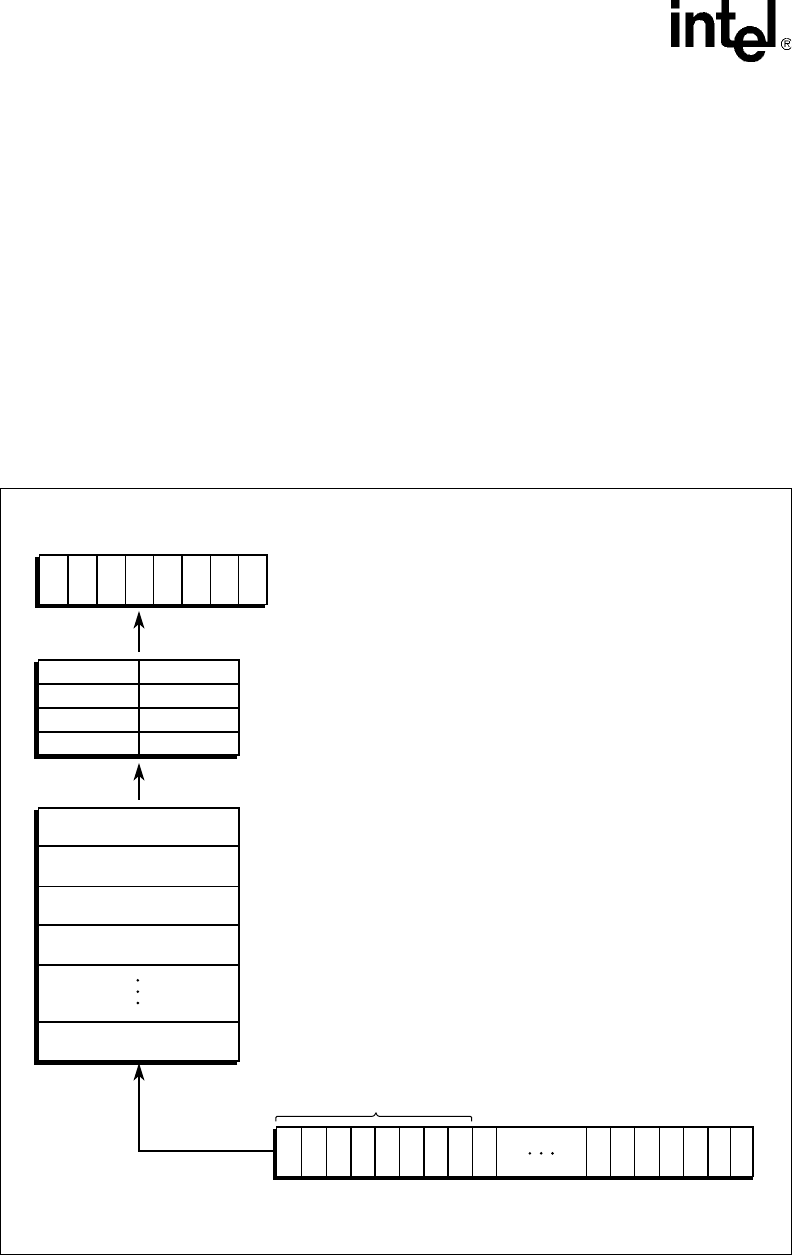

4.5.2.1 Read from RBUF

To analyze the endianness on the media-receive interface and the way in which bytes are arranged

inside RBUF, a brief introduction of how bytes are generated from the serial interface is provided

here. Pipe A denotes the serial stream of data received at the serial interface (SERDES). Bit 0 of

byte 0 comes first, followed by bit 1, etc. Pipe B converts this bit stream into byte stream

byte 0 — byte 7, etc. So, byte 0 currently is the least significant byte received. In Pipe C, before

being transmitted to the SPI-4 interface, these bytes are organized in 16-bit words in big-endian

order where byte 0 is at B[15:8] and byte 1 is at B[7:0].

When the SPI-4 interface inside the IXP2800 received these 16-bit words, they are put into RBUF

in LWBE order where longwords inside one RBUF entry are organized in little-endian order as

shown in one RBUF element in Figure 63. In the least-significant-longword, byte 0 is at a higher

address than byte 3 (therefore, big-endian). Similarly, in the most-significant-longword, byte4 is at

a higher address than byte 7 (therefore, big-endian). While transferring from RBUF to

Microengine, the least significant longword from one RBUF element is transferred first, followed

by the most significant longword into the Microengine transfer registers.

.

Figure 63. Bit, Byte, and Longword Organization in One RBUF Element

A9725-01

Pipe B

Pipe A

Pipe C

SPI-4 Bus

byte 0

RBUF Element

Offset n

byte 1

byte 2

byte 3

byte 7

{7 6 5 4 3 2 1 0}

{31 30 29 28 27 26 25 24}

{23 22 21 20 19 18 17 16}

{15 14 13 12 11 10 9 8}

B63 B31B32 B0

addr15 addr7addr8 addr0

{63 62 61 60 59 58 57 56}

byte 0

byte

4

byte

5

byte

6

byte

7

byte

0

byte

1

byte

2

byte

3

byte 0

0 1 2 3 4 5 678 57 58 59 60 61 62 63

byte 1

byte 2 byte 3

byte 4 byte 5

byte 6 byte 7