316 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

8.9.7 Dynamic De-Skew

The Intel

®

IXP2800 Network Processor supports optional dynamic de-skew for the signals of the

16-bit data interface and the signals of the 4-bit flow control interface or the signals of the 2-bit

SPI-4.2 LVDS status interface. (The flow control interface and the LVDS status interface are

alternate configurations of the same signal balls and pads. They share the same de-skew circuits.)

In both cases, eight evenly-spaced phases of the received clock are generated for each bit time.

As the transition occurs during training a pattern, the best pair of clock phases is identified for

sampling each received signal. An interpolated clock is generated from a pair of clock phases for

each signal and that clock is used as a reference for sampling the data. This provides maximum

quantization error in the sampling of the signals of 6.25%.

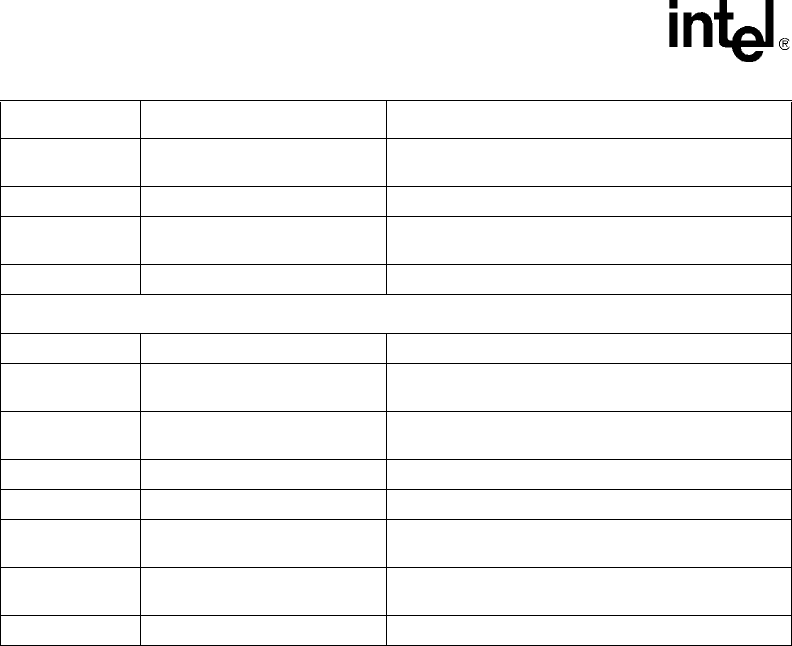

Dead Cycle

Requesting reception of training sequence and no

training sequence pending.

Training Training sequence pending.

SPI

Training sequence not pending and SPI data pending

and not requesting training sequence.

Idle CFrame Dead Cycle Always.

Tracking Other State Machine States

SPI SPI SPI SM not entering CSIX-L1 or Training state.

SoF CWord

SPI SM entering CSIX-L1 state and un-flow-controlled

CFrame pending.

Idle CFrame

SPI SM entering CSIX-L1 state and un-flow-controlled

CFrame not pending.

Training SPI SM entering Training state.

Training Training Training SM not entering CSIX-L1 or Training state.

SoF CWord

Training SM entering CSIX-L1 state and un-flow-

controlled CFrame pending.

Idle CFrame

Training SM entering CSIX-L1 state and un-flow-

controlled CFrame not pending.

SPI Training SM entering SPI state.

Table 116. CSIX-L1 Transmitter State Machine Transitions on CWord Boundaries (Sheet 2 of 2)

Current State Next State Conditions