98 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

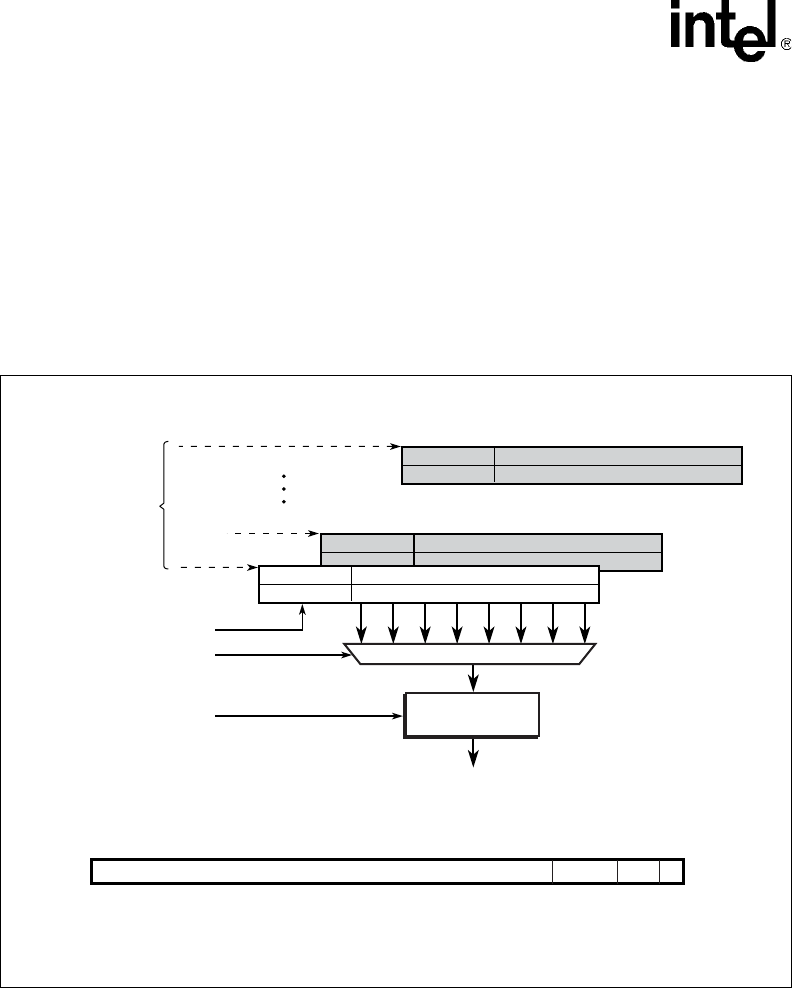

3.6.1.2 Mini-Data Cache Overview

The mini-data cache is a 2-Kbyte, 2-way set associative cache; this means there are 32 sets with

each set containing 2 ways. Each way of a set contains 32 bytes (one cache line) and one valid bit.

There also exist 2 dirty bits for every line, one for the lower 16 bytes and the other one for the

upper 16 bytes. When a store hits the cache, the dirty bit associated with it is set. The replacement

policy is a round-robin algorithm.

Figure 23 shows the cache organization and how the data address is used to access the cache.

The mini-data cache is virtually addressed and virtually tagged and supports the same caching

policies as the data cache. However, lines cannot be locked into the mini-data cache.

Figure 23. Mini-Data Cache Organization

A9692-01

32 bytes (cache line)

Tag

Data Address (Virtual)

Note: CAM = Content Addressable Memory

Set Index

Word Select

Byte Alignment

Sign Extension

Data Word

(4 bytes to Destination Register)

Word

Byte

way 0

Set 31

Set 1

way 1

31 54 21 010 9

Set 0

Byte Select

Tag

This example

shows Set 0 being

selected by the

Set Index

32 bytes (cache line)

way 0

way 1

32 bytes (cache line)

way 0

way 1