Hardware Reference Manual 119

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.9.4.9 Coprocessor Instructions

3.9.4.10 Miscellaneous Instruction Timing

3.9.4.11 Thumb Instructions

The timing of Thumb instructions are the same as their equivalent ARM* instructions. This

mapping can be found in the ARM* Architecture Reference Manual. The only exception is the

Thumb BL instruction when H = 0; the timing in this case would be the same as an ARM* data

processing instruction.

3.10 Test Features

This section gives a brief overview of the Intel XScale

®

core JTAG features. The Intel XScale

®

core provides test features compatible with the IEEE Standard Test Access Port and Boundary Scan

Architecture (IEEE Std. 1149.1). These features include a TAP controller, a 5-bit instruction

register, and test data registers to support software debug. The Intel XScale

®

core also provides

support for a boundary-scan register, device ID register, and other data test registers.

A full description of these features can be found in the Intel

®

IXP2400 and IXP2800 Network

Processor Programmer’s Reference Manual.

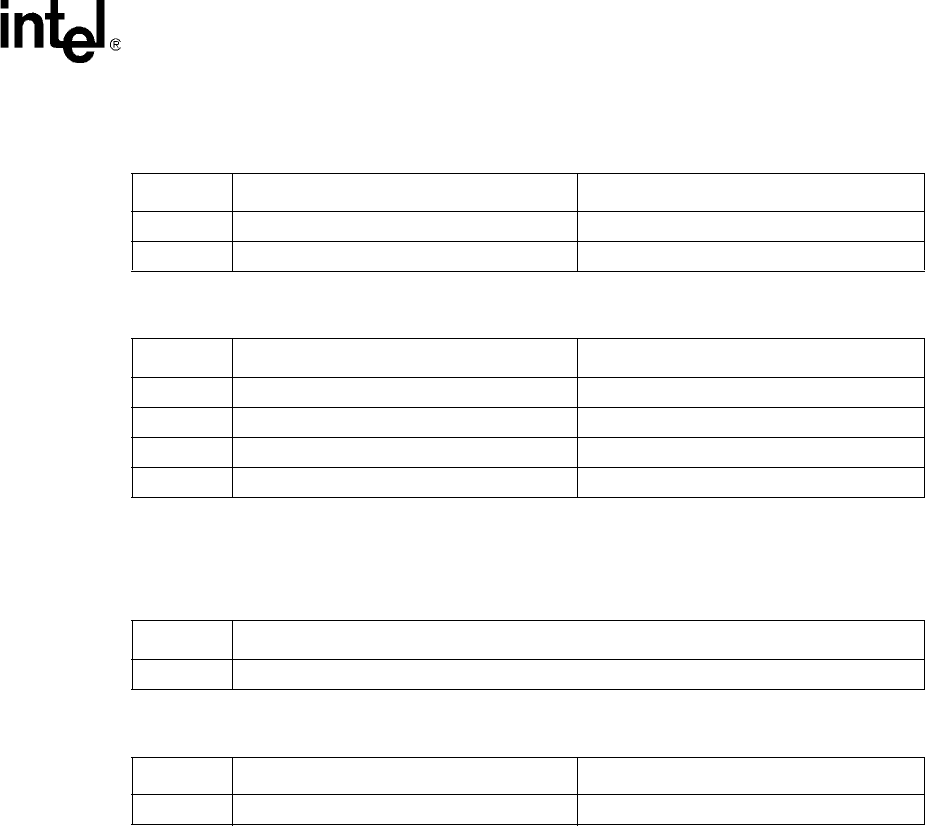

Table 39. CP15 Register Access Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

MRC 4 4

MCR 2 N/A

Table 40. CP14 Register Access Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

MRC 7 7

MCR 7 N/A

LDC 10 N/A

STC 7 N/A

Table 41. SWI Instruction Timings

Mnemonic Minimum latency to first instruction of SWI exception handler

SWI 6

Table 42. Count Leading Zeros Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

CLZ 1 1