80 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.2 Features

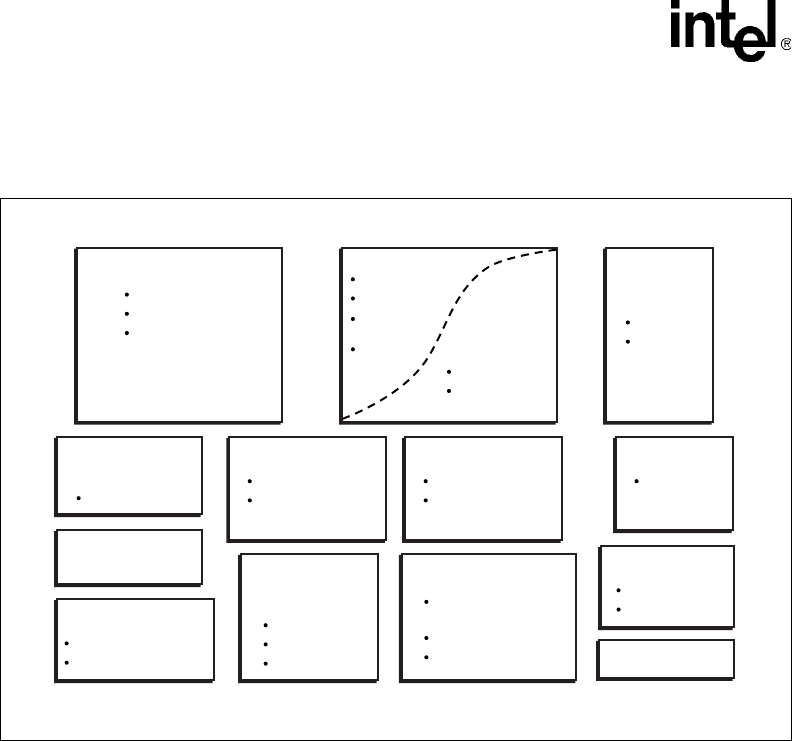

Figure 16 shows the major functional blocks of the Intel XScale

®

core.

3.2.1 Multiply/ACcumulate (MAC)

The MAC unit supports early termination of multiplies/accumulates in two cycles and can sustain a

throughput of a MAC operation every cycle. Architectural enhancements to the MAC support

audio coding algorithms, including a 40-bit accumulator and support for 16-bit packed data.

3.2.2 Memory Management

The Intel XScale

®

core implements the Memory Management Unit (MMU) Architecture specified

in the ARM* Architecture Reference Manual (see the ARM* website at http://www.arm.com).

The MMU provides access protection and virtual to physical address translation. The MMU

Architecture also specifies the caching policies for the instruction cache and data memory.

These policies are specified as page attributes and include:

• identifying code as cacheable or non-cacheable

• selecting between the mini-data cache or data cache

• write-back or write-through data caching

• enabling data write allocation policy

• and enabling the write buffer to coalesce stores to external memory

Figure 16. Intel XScale

®

Core Architecture Features

A9642-01

Instruction Cache

32 Kbytes

32 ways

Lockable by line

Mini-Data

Cache

2 Kbytes

2 ways

Branch Target

Buffer

128 entries

Debug

Hardware Breakpoint

Branch History Table

Power

Management

Idle

Drowsy

Sleep

MAC

Single Cycle

Throughput (16*32)

16-bit SIMD

40-bit Accumulator

Performance

Monitoring

Write Buffer

8 entries

Full coalescing

JTAG

IMMU

32 entry TLB

Fully associative

Lockable by entry

DMMU

32 entry TLB

Fully associative

Lockable by entry

Fill Buffer

4 - 8 entries

Data Cache

Max 32 Kbytes

32 ways

wr-back or

wr-through

Hit under

miss

Data RAM

Max 28 Kbytes

Re-map of

data cache