Hardware Reference Manual 233

Intel

®

IXP2800 Network Processor

SHaC — Unit Expansion

The ring commands operate as outlined in the pseudo-code in Example 32. The operations are

atomic, meaning that multi-word “Gets” and “Puts” do all the reads and writes, with no other

intervening Scratchpad accesses.

Prior to using the Scratchpad rings, software must initialize the Ring registers (by CSR writes). The

Base address of the ring must be written, and also the size field that determines the number of

32-bit words for the Ring.

Note: Detailed information about CSRs is provided in the Intel

®

IXP2400 and IXP2800 Network

Processor Programmer’s Reference Manual.

Writes

For an APB or CAP CSR write, the Scratchpad arbitrates for the S_Pull_Bus, pulls the write data

from the source identified in the instruction (either a Microengine transfer register or an Intel

XScale

®

core write buffer), and puts it into one of the Pull Data FIFOs. It then drives the address

and writes data onto the appropriate bus. CAP CSRs locally decode the address to match their own.

The Scratchpad generates a separate APB device select signal for each peripheral device

(up to 15 devices). If the write is to an APB CSR, the control logic maintains valid signaling until

the APB_RDY_H signal is returned (the APB RDY signal is an extension to the APB bus

specification, specifically added for the Network Processor). Upon receiving the APB_RDY_H

signal, the APB select signal is deasserted and the state machine returns to the idle state between

commands. The CAP CSR bus does not support a similar acknowledge signal on writes since the

Fast Write functionality requires that a write operation be retired on each cycle.

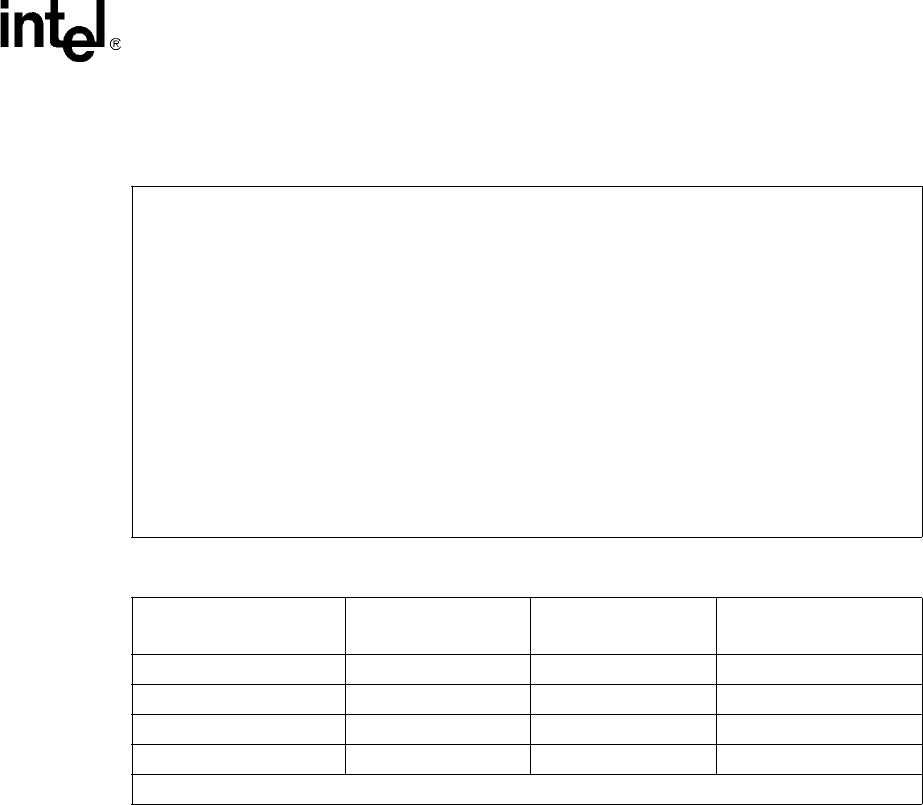

Example 32. Ring Command Pseudo-Code

GET Command

Get(ring, length)

If count[ring] >= length //enough data in the ring?

ME <-- Scratchpad[head[ring]] // each data phase

head[ring]+= length % ringSize

count[ring] -= length

else ME <--nil // 1 data phase signals read off empty list

NOTE: The Microengine signal is delivered with last data. In the case of nil, the signal is delivered with the 1

data phase.

PUT Command

Before issuing a PUT command, it is the responsibility of the Microengine thread issuing the command to make

sure the Ring has enough room.

Put(ring, length)

SRAM[tail[ring]] <-- ME pull data // each data phase

tail[ring]+= length % ringSize

Count[ring] += length

Table 80. Head/Tail, Base, and Full Threshold – by Ring Size

Size

(Number of 32-Bit Words)

Base Address Head/Tail Offset Full Threshold (Entries)

128 13:9 8:2 32

256 13:10 9:2 64

512 13:11 10:2 128

1024 13:12 11:2 256

NOTE: Note that bits [1:0] of the address are assumed to be 00.