60 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Technical Description

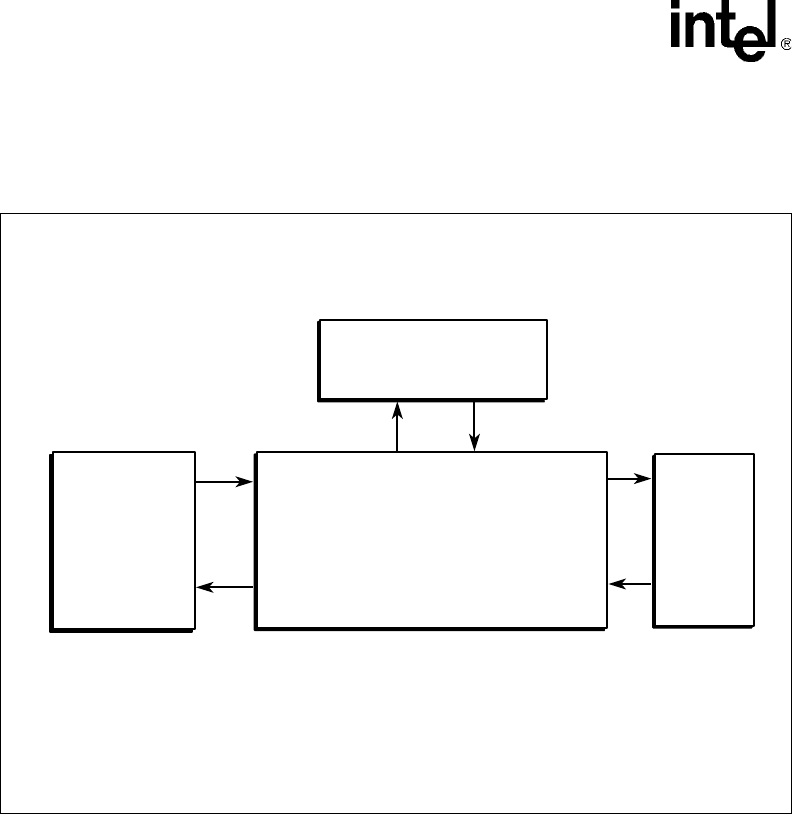

An alternate system configuration is shown in the block diagram in Figure 11. In this case, a single

IXP2800 Network Processor is used for both Ingress and Egress. The bit rate supported would be

less than in Figure 10. A hypothetical Bus Converter chip, external to the IXP2800 Network

Processor is used. The block diagram in Figure 11 is only an illustrative example.

2.7.1 SPI-4

SPI-4 is an interface for packet and cell transfer between a physical layer (PHY) device and a link

layer device (the IXP2800 Network Processor), for aggregate bandwidths of OC-192 ATM and

Packet over SONET/SDH (POS), as well as 10 Gb/s Ethernet applications.

The Optical Internetworking Forum (OIF), www.oiforum.com, controls the SPI-4 Implementation

Agreement document.

SPI-4 protocol transfers data in variable length bursts. Associated with each burst is information

such as Port number (for a multi-port device such as a 10 x 1 GbE), SOP, and EOP. This

information is collected by the MSF and passed to the Microengines.

Figure 11. Full-Duplex Block Diagram

A9357-02

Intel

®

IXP2800

Network Processor

Framing/MAC

Device

(PHY)

UTOPIA-3

or IXBUS

Protocol

Receive and transmit protocol

is SPI-4 and CSIX on transfer-

by-transfer basis.

TDATRDAT

Bus Converter

Rx

Tx

Tx

Rx

Switch

Fabric

CSIX

Protocol

Notes:

The Bus Converter chip receives and transmits both SPI-4 and CSIX protocols from/to Intel

IXP2800 Network Processor. It steers the data, based on protocol, to either PHY device or

Switch Fabric. PHY interface can be UTOPIA-3, IXBUS, or any other required protocol.