Hardware Reference Manual 345

Intel

®

IXP2800 Network Processor

PCI Unit

A 64-bit double Dword with byte enables is pushed into the FBus FIFO from the DMA buffers as

soon as there is data available in the buffer and there is space in the FBus FIFO. The Core logic will

transfer the exact number of bytes to the PCI Bus. The maximum burst size on the PCI bus varies

according to the stepping and is described in Table 127

9.4.1.8 PCI to DRAM Transfer

The DMA channel issues a sequence of PCI read request commands through the FBus address

FIFO to read the precise byte count from PCI.

The DMA engine will continue to load the DMA write buffer with FBus FIFO data as soon as data

is available.

The DMA engine determines the largest size of memory request possible with the current DRAM

address and remaining byte count. It also has to make sure there is enough data in the write buffer

before sending the memory request.

9.4.2 Push/Pull Command Bus Target Interface

Through the command bus target interface, the command bus masters (PCI, Intel XScale

®

core,

and Microengines) can access the PCI Unit internal registers including the local PCI configuration

registers and the local PCI Unit CSRs. Also, the Microengine and the Intel XScale

®

core can issue

transactions on the PCI bus. The requests are generated from the command master to the command

bus arbiter. The arbiter selects a master and sends it a grant. That master then sends a command,

which is passed through by the arbiter.

PCI Unit will issue the push and pull data responses to the SRAM push/pull data buses. When the

read command is received, the PCI Unit will issue the push data request on the SRAM push data

bus. When the write command is received, PCI Unit will issue the pull command on the SRAM

pull data bus.

9.4.2.1 Command Bus Master Access to Local Configuration Registers

The configuration register within the PCI unit can be accessed by push/pull command bus access to

configuration space through the FBus interface of the PCI core. When the IXP2800 Network

Processor is a PCI host, these registers have to be accessed through this internal path and no PCI

bus cycle will be generated.

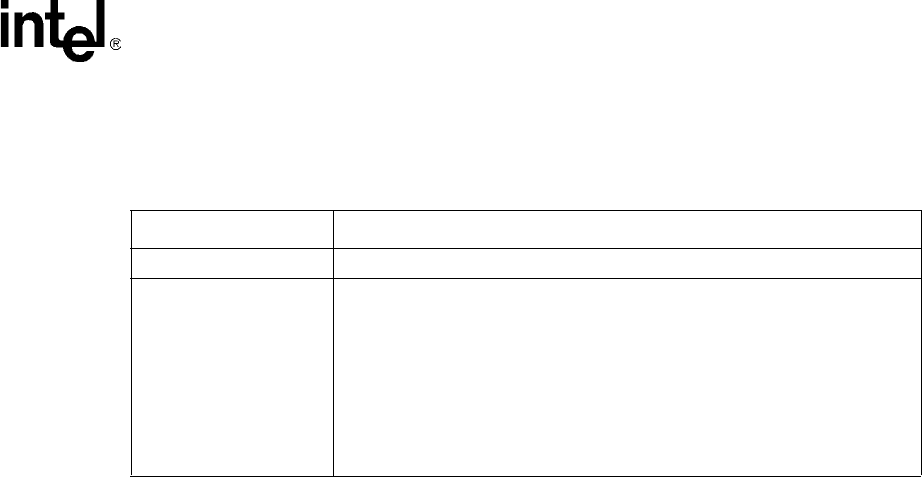

Table 127. PCI Maximum Burst Size

Stepping Description

A Stepping The maximum burst size is 64 bytes.

B Stepping

The maximum burst size can be greater than 64 bytes for certain operations.

The register PCI_IXP_PARAM configures the burst length for target write

operations.

The register CHAN_#_CONTROL configures the burst length for DMA read and

write operations.

The register PCI_CONTROL configures the atomic feature for target write

operations of 64 bytes or fewer.

Note: Bursts longer than 64 bytes are not supported for PCI target read

operations.