170 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Microengines

The Microengine is in Idle state whenever no Context is running (all Contexts are in either Inactive

or Sleep states). This state is entered:

1. After reset (because CTX_Enable Local CSR is clear, putting all Contexts into Inactive states).

2. When a context swap is executed, but no context is ready to wakeup.

3. When a

ctx_arb[bpt] instruction is executed by the Microengine (this is a special case of

condition 2 above, since the

ctx_arb[bpt] clears CTX_Enable, putting all Contexts into

Inactive states).

The Microengine provides the following functionality during Idle state:

1. The Microengine continuously checks if a Context is in Ready state. If so, a new Context

begins to execute. If no Context is Ready, the Microengine remains in the Idle state.

2. Only the ALU instructions are supported. They are used for debug via special hardware

defined in number 3 below.

3. A write to the Ustore_Addr Local CSR with the Ustore_Addr[ECS] bit set, causing the

Microengine to repeatedly execute the instruction pointed by the address specified in the

Ustore_Addr CSR. Only the ALU instructions are supported in this mode. Also, the result of

the execution is written to the ALU_Out Local CSR rather than a destination register.

4. A write to the Ustore_Addr Local CSR with the Ustore_Addr[ECS] bit set, followed by a

write to the Ustore_Data Local CSR loads an instruction into the Control Store. After the

Control Store is loaded, execution proceeds as described in number 3 above. Note that the

write to Ustore_Data causes Ustore_Addr to increment, so it must be written back to the

address of the desired instruction.

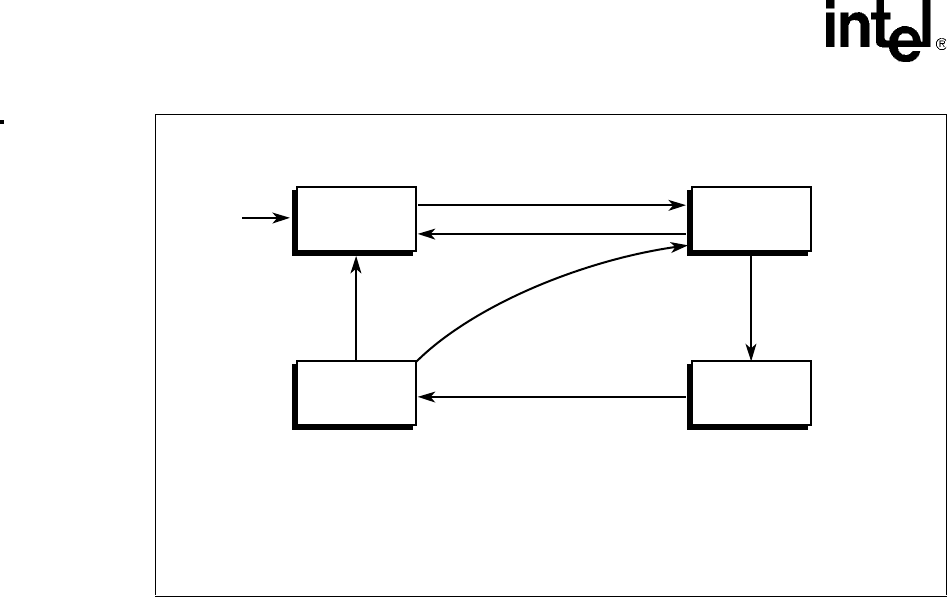

Figure 57. Context State Transition Diagram

A9352-03

Inactive Ready

CTX_ENABLE bit is set by

Intel XScale

®

Core

CTX_ENABLE bit is cleared

CTX_ENABLE

bit is cleared

Reset

Sleep Executing

Context executes

CTX Arbitration instruction

Executing Context goes

to Sleep state, and this

Context is the highest

round-robin priority.

E

x

t

e

r

n

a

l

E

v

e

n

t

S

i

g

n

a

l

a

r

r

i

v

e

s

Note:

After reset, the Intel XScale

®

Core processor must load the starting address of the CTX_PC, load the

CTX_WAKEUP_EVENTS to 0x1 (voluntary), and then set the appropriate CTX_ENABLE bits to begin

executing Context(s).