386 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

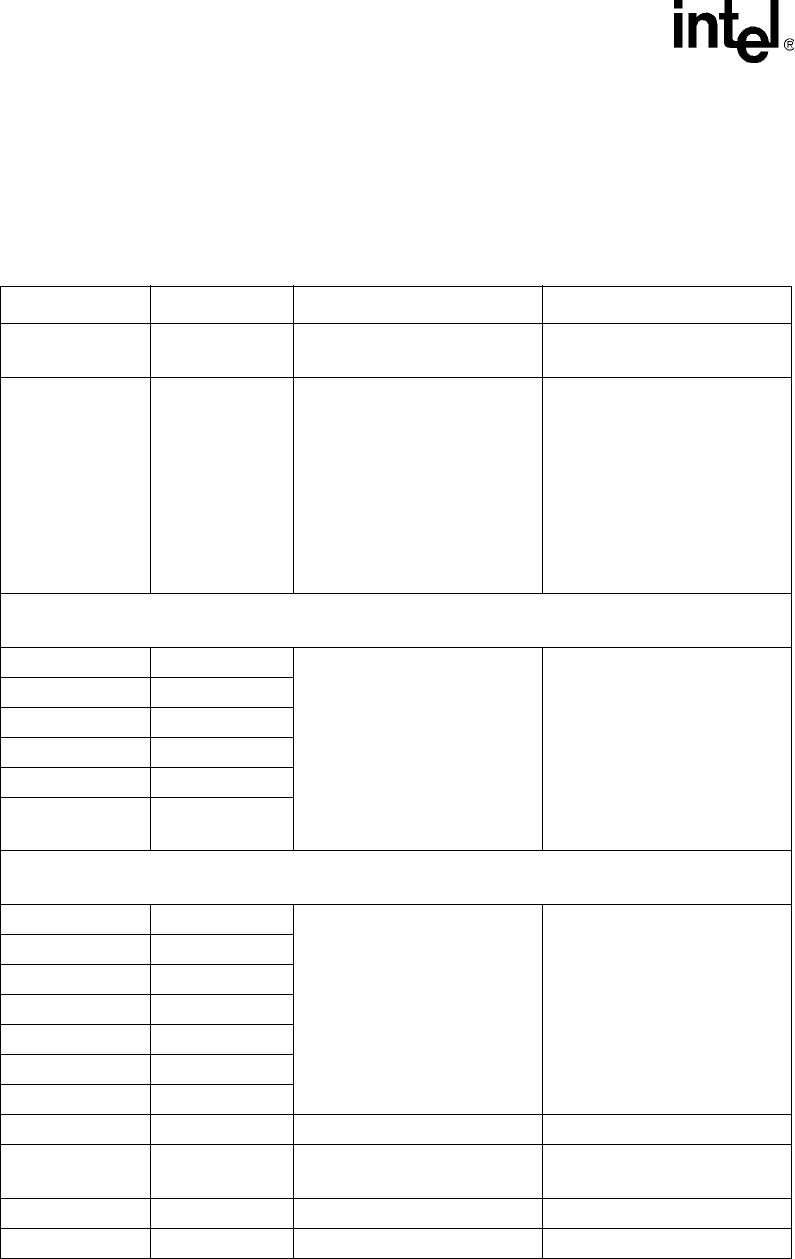

11.4.3 Design Block Select Definitions

Once an event is defined, its definition must remain consistent between products. If the definition

changes, it should have a new event selection code. This document contains the master list of all

ESCs in all CHAP-enabled products. Not all of the ESCs in this document are listed in numerical

order. The recommendation is to group similar events within the following ESC ranges.

See Table 153.

Table 153. PMU Design Unit Selection (Sheet 1 of 2)

Target Device Target ID PMU Design Group Block # Description

Null xxx xxx 0000

Null (False) Event

PMU_Counter xxx xxx

0001

(PMU)

CHAP Counters Internal

Threshold Events

Event bit 0 CHAP Counter 0

Event bit 1 CHAP Counter 1

Event bit 2 CHAP Counter 2

Event bit 3 CHAP Counter 3

Event bit 4 CHAP Counter 4

Event bit 5 CHAP Counter 5

SRAM Group

SRAM_DP1 001 001

0010

(SRAM Group)

one and only one will be

selected from same group

SRAM channel 0

SRAM channel 1

SRAM channel 2

SRAM channel 3

SRAM d-push

SRAM d-pull

SRAM_DP0 001 010

SRAM_CH3 001 011

SRAM_CH2 001 100

SRAM_CH1 001 101

SRAM_CH0 001 110

DRAM Group

DRAM_CR1 010 000

0011

(DRAM)

one and only one will be

selected from same group

DRAM channel 0

DRAM channel 1

DRAM channel 2

DRAM d-push

DRAM d-pull

DRAM_CR0 010 001

DRAM_DPLA 010 010

DRAM_DPSA 010 011

DRAM_CH2 010 100

DRAM_CH1 010 101

DRAM_CH0 010 110

XPI 000 001

0100

(XPI)

XPI

SHaC 000 010 0101

MSF 000 011 0110 Media