Hardware Reference Manual 323

Intel

®

IXP2800 Network Processor

PCI Unit

PCI functions not supported by the PCI Unit include:

• IO Space response as a target

• Cacheable memory

• VGA palette snooping

• PCI Lock Cycle

• Multi-function devices

• Dual Address cycle

9.2.2 IXP2800 Network Processor Initialization

When the IXP2800 Network Processor is a target, the internal CSR, DRAM, or SRAM address is

generated when the PCI address matches the appropriate base address register. The window sizes to

the SRAM and DRAM Base Address Registers (BARs) can be optionally set by PCI_SWIN and

PCI_DWIN strap pins or mask registers depending on the state of the PROM_BOOT signal.

There are two initialization modes supported. They are determined by the PROM_BOOT signal

sampled on the de-assertion edge of Chip Reset. If PROM_BOOT is asserted, then there is a boot

prom in the system. The Intel XScale

®

core will boot from the prom and be able to program the

BAR space mask registers. If PROM_BOOT is not asserted, the Intel XScale

®

core is held in reset

and the BAR sizes are determined by strap pins.

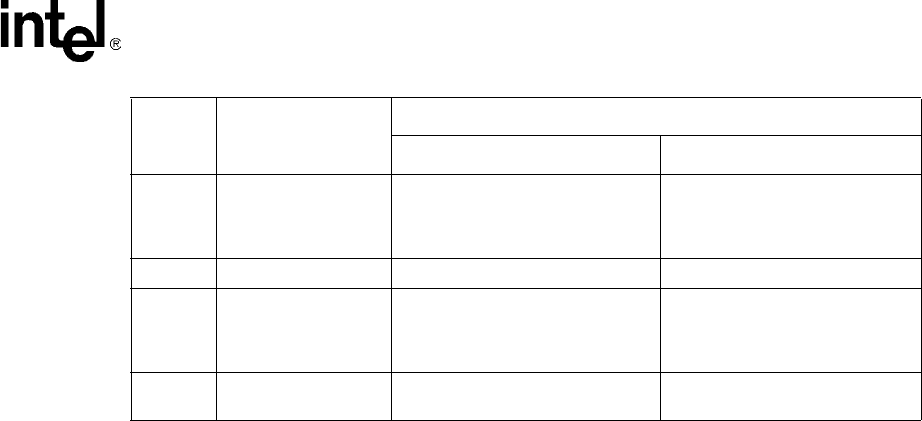

0xC

Memory Read

Multiple

Aliased as Memory Read except

SRAM accesses where the number

of Dwords to read is given by the

cache line size.

Supported

0xD Reserved — —

0xE Memory read line

Aliased as Memory Read except

SRAM accesses where the number

of Dwords to read is given by the

cache line size.

Supported

0xF

Memory Write and

Invalidate

Aliased as Memory Write. Not Supported

Table 119. PCI Commands (Sheet 2 of 2)

C_BE_L Command

Support

Target Initiator