Hardware Reference Manual 275

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

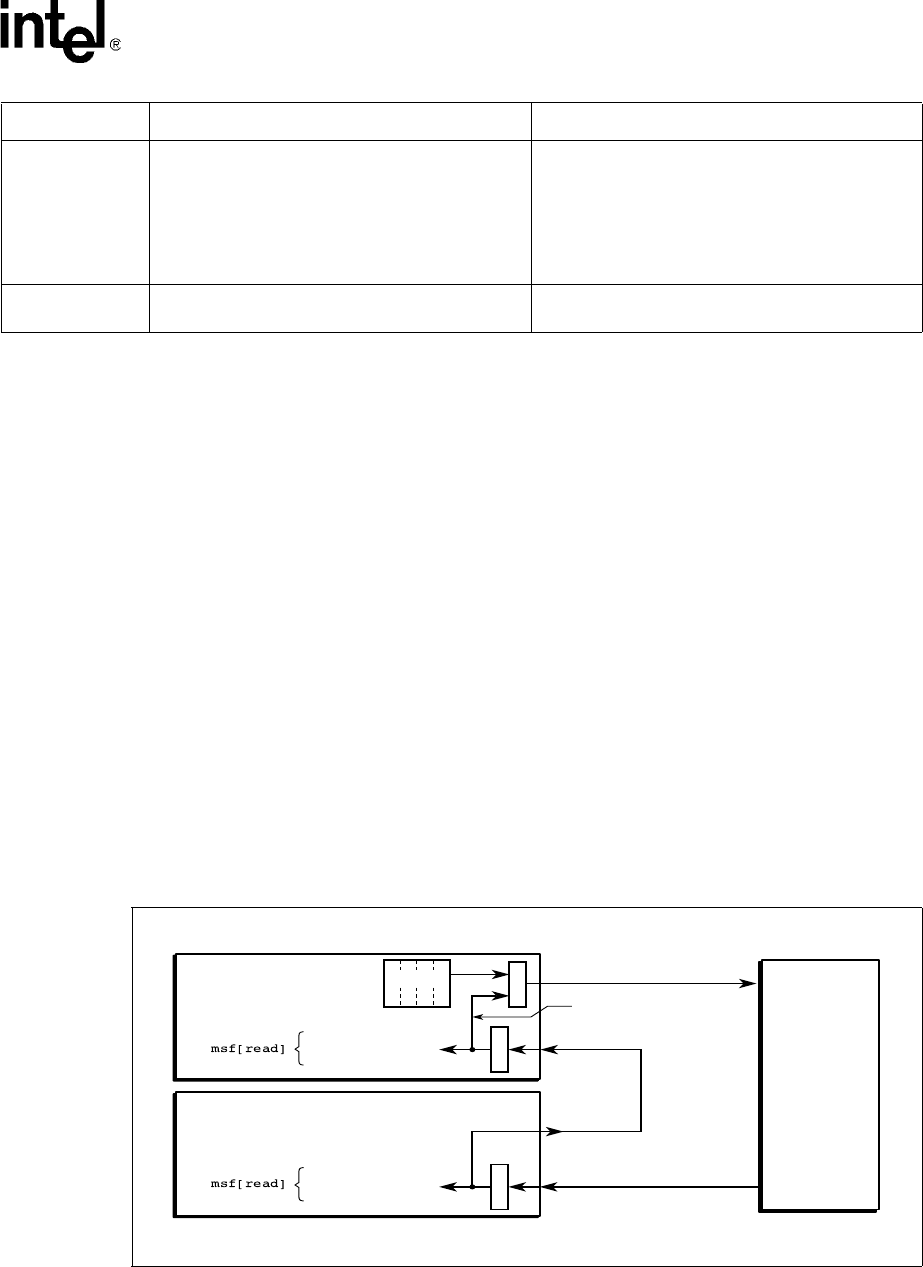

8.5 CSIX Flow Control Interface

This section describes the Flow Control Interface. Section 8.2 and Section 8.3 of this chapter also

contain descriptions of how those functions interact with Flow Control. There are two modes —

Full Duplex, where flow control information goes from Egress IXP2800 Network Processor to the

Ingress IXP2800 Network Processor, and Simplex mode, where the information from the Switch

Fabric is sent directly to the Ingress IXP2800 Network Processor, and from the Egress IXP2800

Network Processor to the Switch Fabric.

8.5.1 TXCSRB and RXCSRB Signals

TXCSRB and RXCSRB are used only in Full Duplex mode. (See Figure 97.) They send

information from the Egress to the Ingress IXP2800 Network Processor for two reasons:

1. Pass the CSIX Ready Field (link-level flow control) from the Switch Fabric to the Ingress

IXP2800. The information is used by the Ingress IXP2800’s transmit control logic to stop

transmission of CFrames to the Switch Fabric.

2. Set the value of the Ready field sent from the Ingress IXP2800 to the Switch Fabric. This is to

inform the Switch Fabric to stop transmitting CFrames to the Egress IXP2800, based on

receive buffer resource availability in the Egress IXP2800.

Remove data from

element

Microcode moves data from the element to DRAM

using the dram[rbuf_rd] instruction and to

Microengine registers using the

msf[read]

instruction.

Hardware transmits information from the element to

the Tx pins. Transmission of elements is in FIFO

order within each partition; that is an element will be

transmitted only when all preceding elements in that

partition have been transmitted.

Choice of element to transmit among partitions is

round-robin.

Return element to

Free List

Microcode writes to Rx_Element_Done with the

number of the element to free.

Microengine software uses the TX_Sequence_n

CSRs to track elements that have been transmitted.

Table 102. Summary of RBUF and TBUF Operations (Sheet 2 of 2)

Operation RBUF TBUF

Figure 97. CSIX Flow Control Interface — TXCSRB and RXCSRB

A9762-01

TDAT

RXCSRB

Link Level Flow Control

TXCSRB

RDAT

FC_Ingress_Status

CSR

Ingress

Intel

®

IXP2800

Network Processor

Egress

Intel IXP2800

Network Processor

Switch

Fabric

FC_Egress_Status

CSR

TBUF