122 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

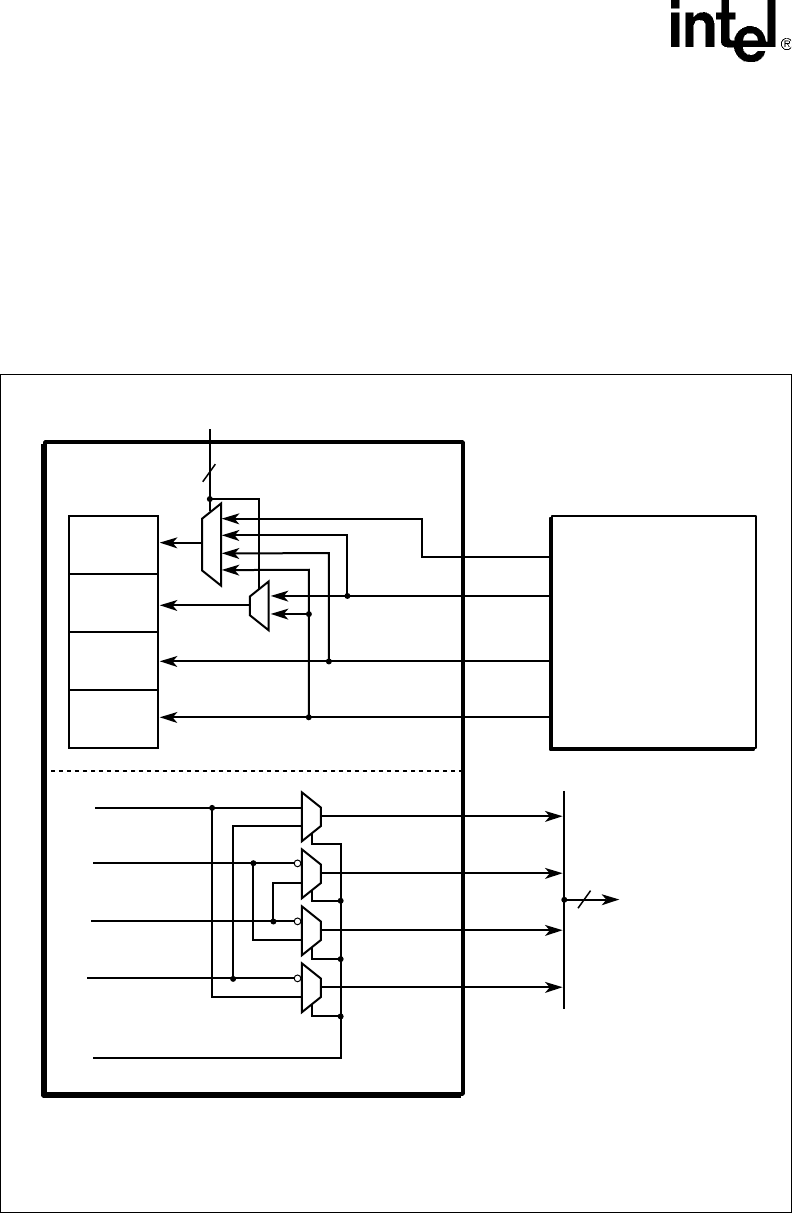

16-Bit (Word) Read

When reading a word, the Intel XScale

®

core generates the byte_enable that corresponds to the

proper byte lane as defined by the endianness setting. Figure 25 summarizes byte enable generation

for this mode.

The 4-to-1 multiplexer steers byte lane 0 or byte lane 2 into the byte 0 location of the read register

inside the Intel XScale

®

core. The 2-to-1 multiplexer steers byte lane 1 or byte lane 3 into the

byte 1 location of the read register inside the Intel XScale

®

core. The Intel XScale

®

core does not

allow word access to an odd-byte address. Select signals for the multiplexer are generated based on

endian setting and ByteEnable generated by the Intel XScale

®

core, as defined in Figure 24.

Table 46 summarizes byte-enable generation for this mode.

Figure 24. Byte Steering for Read and Byte-Enable Generation by the Intel XScale

®

Core

A9694-03

0

1

0

1

2

3

0

1

0

1

0

1

0

1

BE0

BE1

BE2

BE3

X_BE[0]

X_BE[1]

X_BE[2]

X_BE[3]

Big Endian =0

Little Endian = 1

D[7:0]

M[7:0]

M[15:8]

M[23:16]

M[31:24]

S0

S1

X[7:0] Byte 0

X[31:24] Byte 3

X[23:16] Byte 2

X[15:8] Byte 1

D[15:8]

D[23:16]

D[31:24]

Intel XScale

®

Core

Intel

®

IXP2800

Core Gasket

Notes: For 32-bit Operation S0[3:0] = 0001; S1[1:0] = 01

Otherwise: S0[3:0] = X_BE[3:0]; S1[1:0] = X_BE[1:2]