Hardware Reference Manual 145

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

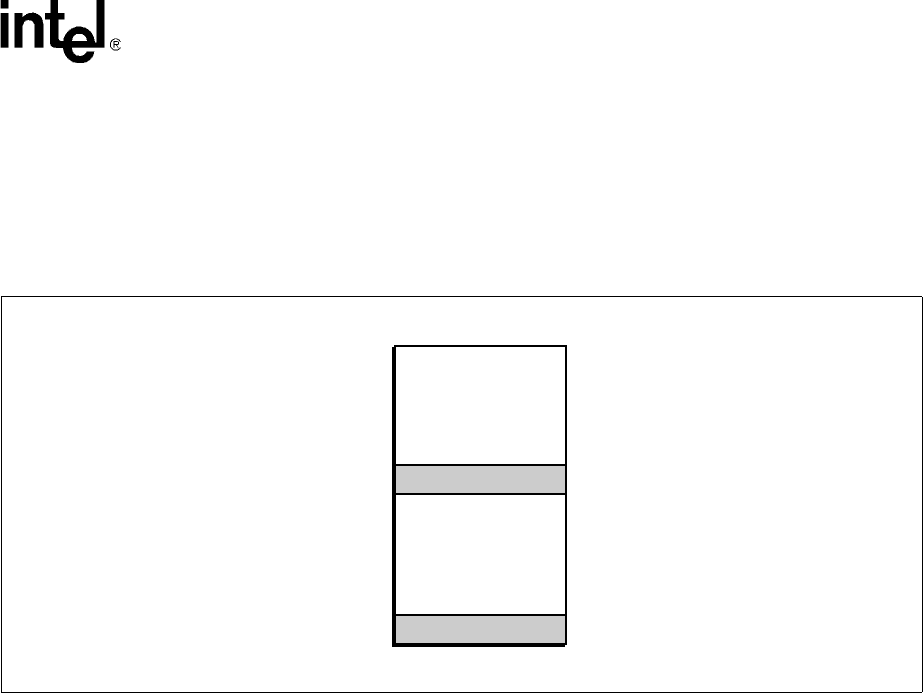

3.12.7.4 Address Space

The total address space is defined as 64 Mbytes, which is further divided into two segments of

32 Mbytes each. Two devices can be connect to this bus. If these peripheral devices have a density

of 256 Mbits (32 Mbytes) each, all the address space is going to be filled like a contiguous address

space. However, if a small capacity device is used (like a device of 4, 8, or 16 MBytes), there will

be a memory hole left in between these two devices. Figure 36 is a 4-Mbyte memory example.

Trying to read the space in between, you will get the repeating value for each 4-Mbyte location

3.12.7.5 Slowport Interfacing Topology

Figure 37 demonstrates one of the topologies used to connect to an 8-bit device. From the diagram,

we can observe that address is shifted out eight bits at a time and buffered into three 74F377 or

equivalent tri-state buffer devices in three consecutive clock cycles. These buffers also output

separately to form a 25-bit wide address bus to address the 8-bit devices. The data are expected to

be driven out after the address has been placed into the buffers.

There are two devices shown in Figure 37. The top one is the fix-timed device, while the lower

one, self-timing device. For the self-timing device, the access latency depends on the SP_ACK_L

responded back from this device.

Three extra signals, SP_CP, SP_OE_L, and SP_DIR, are added to pack and unpack the data when a

16-bit or 32-bit device is hooked up to Slowport. They are used for special application only as

described below.

Figure 36. Address Space Hole Diagram

A9705-01

3FFFFFFh

23FFFFFh

2000000h

03FFFFFh

0000000h

4 MB

4 MB