Hardware Reference Manual 381

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

11.2.1 APB Peripheral

The APB is part of the AMD* controller Bus Architecture (AMBA) hierarchy of buses that is

optimized for minimal power consumption and reduced design complexity. The PMU needs to

operate as an APB peripheral, interfacing with rest of the chip via the APB. The PMU needs to

have an APB interface unit, which can perform a APB reads and writes to enable data transfer to

and from the PMU registers.

11.2.2 CAP Description

11.2.2.1 Selecting the Access Mode

The CAP selects the appropriate access mode based on the COMMAND and ADDRESS fields

from the Command Bus.

11.2.2.2 PMU CSR

Please refer to Intel IXP2400 and IXP2800 Network Processor Programmer's Reference Manual.

11.2.2.3 CAP Writes

For an APB write, CAP arbitrates for the S_Pull_Bus, pulls the write data from the source

identified in PP_ID (either a Microengine transfer register or Intel XScale

®

core write buffer), and

puts it into the CAP Pull Data FIFO. It then drives the address and writes data onto the appropriate

bus. CAP CSRs locally decode the address to match their own. CAP generates a separate APB —

devices select signal for each CAP device (up to 15 devices). If the write is to an APB CSR, the

Control Logic maintains valid signaling until the APB_RDY_H signal is returned. (The APB RDY

signal is an extension to the APB specification specifically added for the Network Processor).

CAP supports write operations with burst counts greater than 1. CAP looks at the length field on

the command bus and breaks each count into a separate APB write cycle, incrementing the CSR

number for each bus access.

11.2.2.4 CAP Reads

For an APB read, CAP drives the address, write, select, and enable signals, and waits for the

acknowledge signal (APB_RDY_H) from the APB device. For a CAP CSR read, CAP drives the

address, which controls a tree of multiplexers to select the appropriate CSR. CAP then waits for the

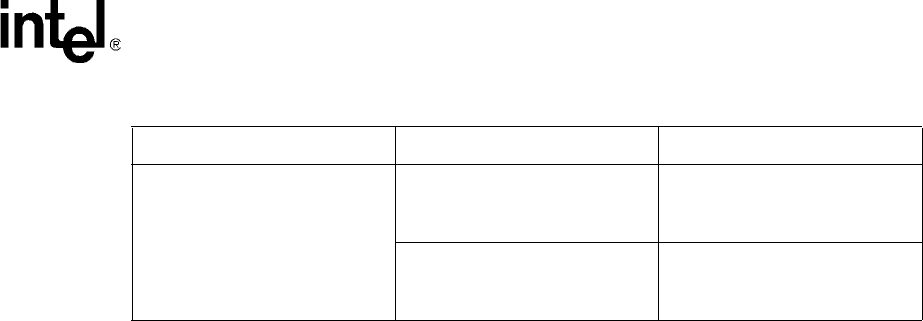

Table 151. APB Usage

Accessing Read Operation Write Operation

APB Peripheral

Access Method:

• Microengine: csr[read]

• Intel XScale

®

core: ld

Access Method:

• Microengine: csr[write]

• Intel XScale® core: st

Bus Usages:

• Read source: APB

• Write destination: Push bus

Bus Usages:

• Read source: Pull Bus

• Write destination: APB