Hardware Reference Manual 369

Intel

®

IXP2800 Network Processor

Clocks and Reset

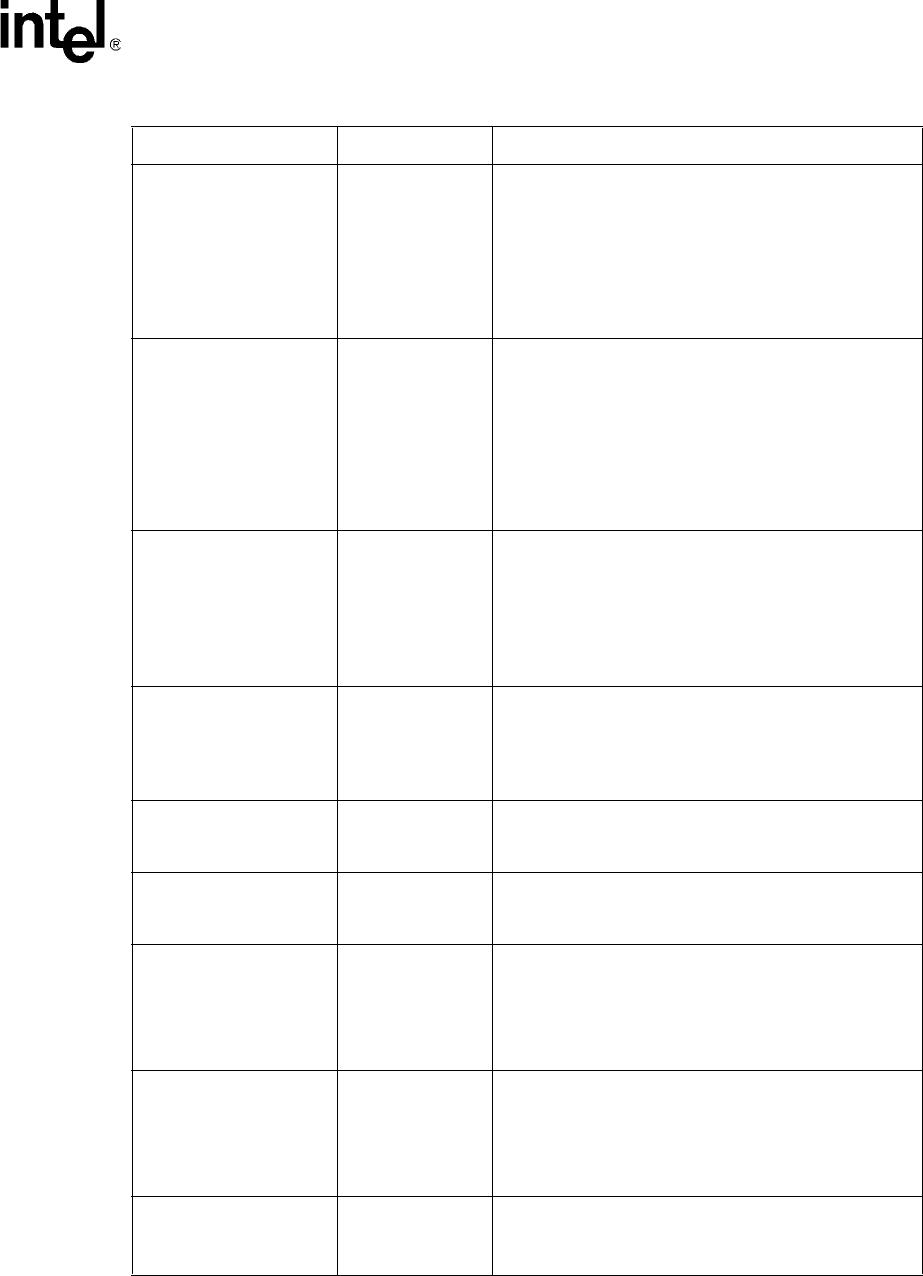

Table 149. IXP2800 Network Processor Strap Pins

Signal Name Description

CFG_RST_DIR RST_DIR

PCI_RST direction pin: (Also called PCI_HOST) Need to

be a dedicated pin.

1—IXP2800 Network Processor is the host supporting

central function. PCI_RST_L is output.

0—IXP2800 Network Processor is not central function.

PCI_RST_L is input.

This pin is stored at XSC[31] (XScale_Control register) at

the trailing edge of reset.

CFG_PROM_BOOT GPIO[0]

PCI PROM BOOT Pin:

1—IXP2800 Network Processor will boot from PROM:

Whether Intel XScale

®

core will configure the system or not

will be defined by CFG_PCI_BOOT_HOST strap option.

0—IXP2800 Network Processor will not boot from PROM.

So after host has downloaded image od boot code into

DRAM, Intel XScale

®

core will boot from DRAM address 0.

This pin is stored at XSC[29] (XScale_Control register) at

the trailing edge of reset.

CFG_PCI_BOOT_HOST GPIO[1]

PCI BOOT HOST Pin:

1—IXP2800 Network Processor will configure the PCI

system.

0—IXP2800 Network Processor will not configure the PCI

system.

This pin is stored at XSC[28] (XScale_Control register) at

the trailing edge of reset.

CFG_PCI_ARB GPIO[2]

PCI Arbiter Pin:

1—IXP2800 Network Processor is the arbiter on the PCI

bus.

0—IXP2800 Network Processor is not the arbiter on the

PCI bus.

PLL_MULT[5:0] SP_AD[5:0]

PLL Multiplier

Valid values are 010000-110000 for a multiplier range of 16

– 48. Other values will result in undefined behavior by PLL.

RESET_OUT_STRAP SP_AD[7]

When 1: nRESET_OUT is removed after PLL locks.

When 0: nRESET_OUT is removed by software using bit

IXP_RESET0[17].

CFG_PCI_SWIN[1:0] GPIO[6:5]

SRAM Bar Window:

11—SRAM BAR size of 256 Mbytes

10—SRAM BAR size of 128 Mbytes

01—SRAM BAR size of 64 Mbytes

00—SRAM BAR size of 32 Mbytes

CFG_PCI_DWIN[1:0] GPIO[4:3]

DRAM BAR Window:

11—DRAM BAR size of 1024 Mbytes

10—DRAM BAR size of 512 Mbytes

01—DRAM BAR size of 256 Mbytes

00—DRAM BAR size of 128 Mbytes

CFG_MSF_FREQ_SEL SP_AD[6]

Select source of MSF Tx Clock:

0—TCLK_Ref input pin

1—Internally generated clock