Hardware Reference Manual 181

Intel

®

IXP2800 Network Processor

Microengines

4.5.1 Microengine Endianness

Microengine operation from an “endian” point of view can be divided into following categories:

• Read from RBUF (64 bits)

• Write to TBUF (64 bits)

• Read/write from/to SRAM

• Read/write from/to DRAM

• Read/write from/to SHaC and other CSRs

• Write to Hash

4.5.1.1 Read from RBUF (64 Bits)

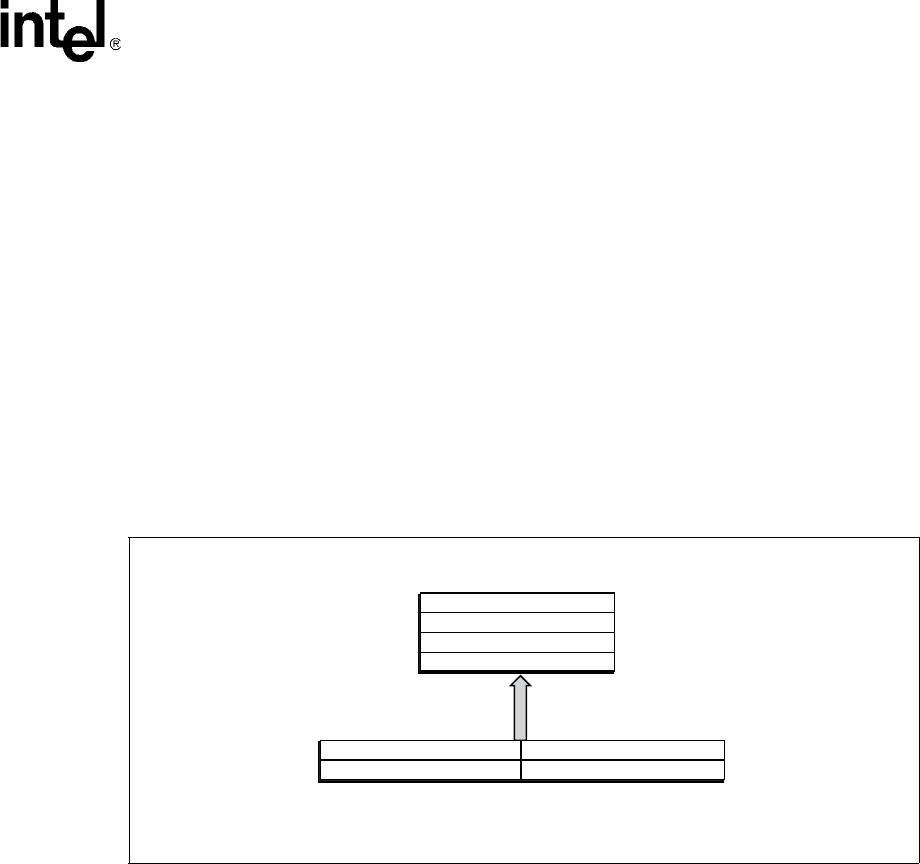

Data in RBUF is arranged in LWBE order. Whenever the Microengine reads from RBUF, the low

order longword (LDW0) is transferred into Microengine transfer register 0 (treg0), the high order

longword (LDW1) is transferred into treg1, etc. This is explained in Figure 60.

Figure 60. Read from RBUF (64 Bits)

A8941-01

0123

4567

8 9 10 11

12 13 14 15

4567

12 13 14 15

0123

MicroEngine

LDW1 LDW0

RBUF

treg0

treg1

treg2

treg3

8 9 10 11