336 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

PCI Unit

Note: The IXP2800/IXP2850 always disconnects after transferring 16-bytes for DRAM target reads. The

PCI core will also disconnect at a 64-byte address boundary.

The PCI core resets the read FIFO before issuing a memory read data request on FBus. The PCI

core will disconnect at the 64-byte address boundary.

9.3.4 Mailbox and Doorbell Registers

Mailbox and Doorbell registers provide hardware support for communication between the Intel

XScale

®

core and a device on the PCI Bus.

Four mailbox registers are provided so that messages can be passed between the Intel XScale

®

core

and a PCI device. All four registers are 32 bits and can be read and written with byte resolution

from both the Intel XScale

®

core and PCI. How the registers are used is application dependent and

the messages are not used internally by the PCI Unit in any way. The mailbox registers are often

used with the Doorbell interrupts.

Doorbell interrupts provide an efficient method of generating an interrupt as well as encoding the

purpose of the interrupt. The PCI Unit supports an Intel XScale

®

core Doorbell register that is used

by a PCI device to generate an Intel XScale

®

core FIQ and a separate PCI Doorbell register that is

used by the Intel XScale

®

core to generate a PCI interrupt. A source generating the Doorbell

interrupt can write a software defined bitmap to the register to indicate a specific purpose. This

bitmap is translated into a single interrupt signal to the destination (either a PCI interrupt or a

IXP2800 Network Processor interrupt). When an interrupt is received, the Doorbell registers can

be read and the bit mask can be interpreted. If a larger bit mask is required than that is provided by

the Doorbell register, the Mailbox registers can be used to pass up to four 32-bit blocks of data.

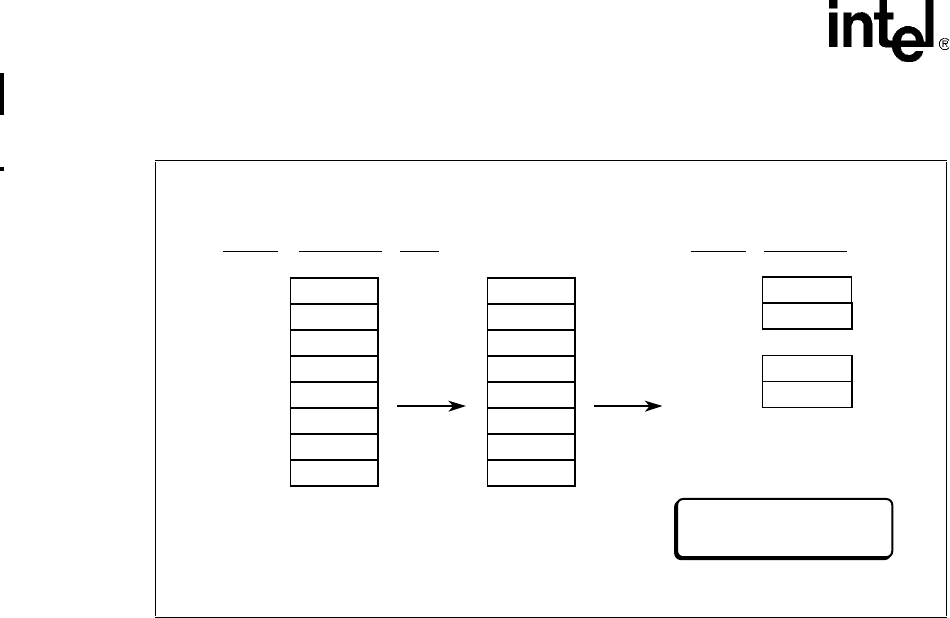

Figure 123. Example of Target Read from DRAM Using 64-Byte Burst

A9770-02

11111111

11111111

11111111

11111111

11111111

11111111

11111111

11111111

00000000

00000000

00000000

00000000

Memory Transfer Internal

Bus Data

PCI Bus

Byte Lane

Swap

Slave Read Burst from memory

Starting address = 0x0

Transfer Size - 32 bytes

Byte EnablesAddress Size

Byte Enables

16 Byte

0x0

Address

0x00

0x10

0x10

Disconnect