Hardware Reference Manual 271

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

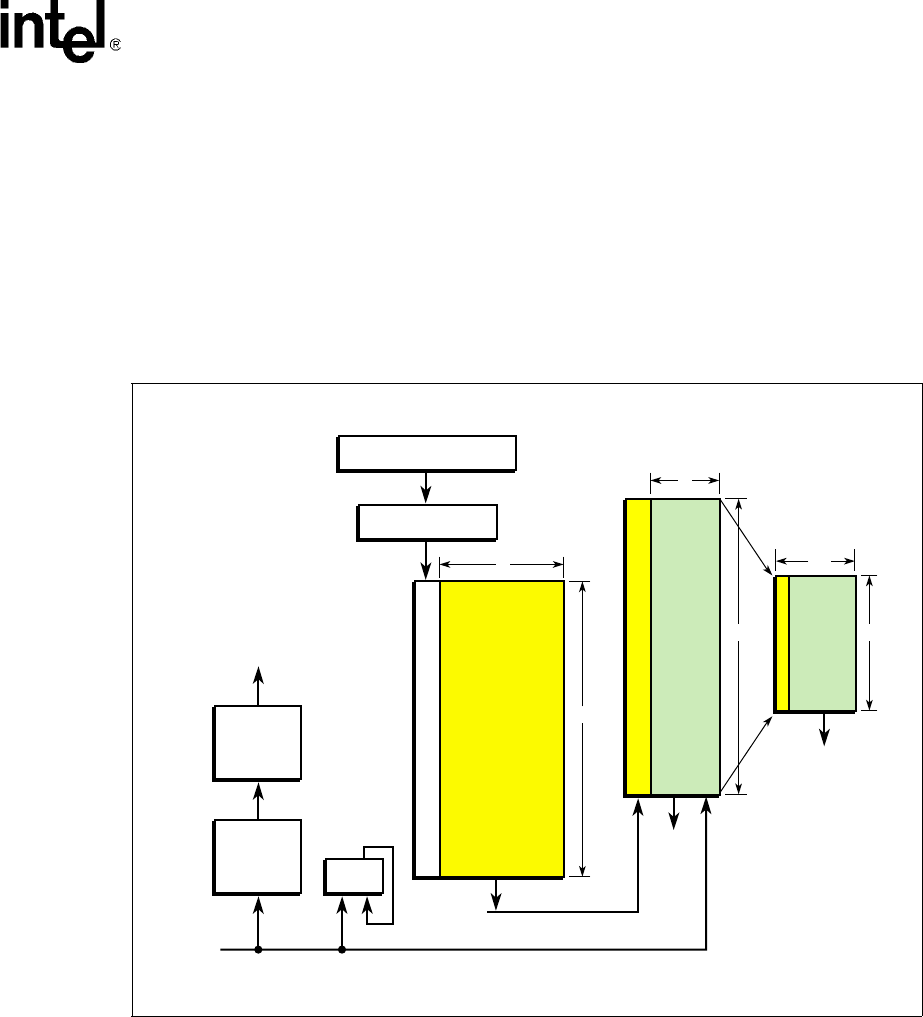

8.3.4.1 SPI-4

FIFO status information is sent periodically over the TSTAT signals from the PHY to the Link

Layer device, which is the IXP2800 Network Processor. (The RXCDAT pins can act as TSTAT

based on the MSF_Tx_Control[TSTAT_Select] bit.) The FIFO status of each port is encoded in a

2-bit data structure — code 0x3 is used for framing the data, and the other three codes are valid

status values, which are interpreted by Microengine software.

The FIFO status words are received according to a repeating calendar sequence. Each sequence

begins with the framing code to indicate the start of a sequence, followed by the status codes,

followed by a DIP-2 parity code covering the preceding frame. The length of the calendar, as well

as the port values, are defined in this section, and shown in Figure 96.

Tx_Port_Status_# is a register file containing 256 registers, one for each of the SPI-4.2 ports. The

port status is updated each time a new calendar status is received for each port, according to the

mode programmed in MSF_Tx_Control[Tx_Status_Update_Mode]. The Tx_Port_Status_#

register file holds the latest received status for each port, and can be read by CSR reads.

There are 16 Tx_Multiple_Port_Status_# registers. Each aggregates the status for each group of

16 ports. These registers provide an alternative method for reading the FIFO status of multiple

ports with a single CSR read. For example, Tx_Multiple_Port_Status_0 contains the 2-bit status

for ports 0 – 16, and provides the same status as reading the individual registers,

Tx_Port_Status_0 through Tx_Port_Status_15.

Figure 96. Tx Calendar Block Diagram

A9761-02

Tx_Calendar_Length

Calendar Counter

8

256

TSTAT

CSR

Reads

CSR

Reads

To

MSF_Interrupt_Status

and MSF_Tx_Control

Registers

Parity

Start of

Frame

Detect

Frame

Pattern

Counter

Tx

Port

Status

256

2

Tx

Multiple

Port

Status

16

32

Tx_Calendar