Hardware Reference Manual 235

Intel

®

IXP2800 Network Processor

SHaC — Unit Expansion

7.1.2.3.3 Clocks and Reset

Clock generation and distribution is handled outside of CAP and is dependent on the specific chip

implementation. Separate clock rates are required for CAP CSRs/Push/Pull Buses and ARB since

APB devices tend to run slower. CAP provides reset signals for the CAP CSR block and APB

devices. These resets are based on the system reset signal and synchronized to the appropriate bus

clock.

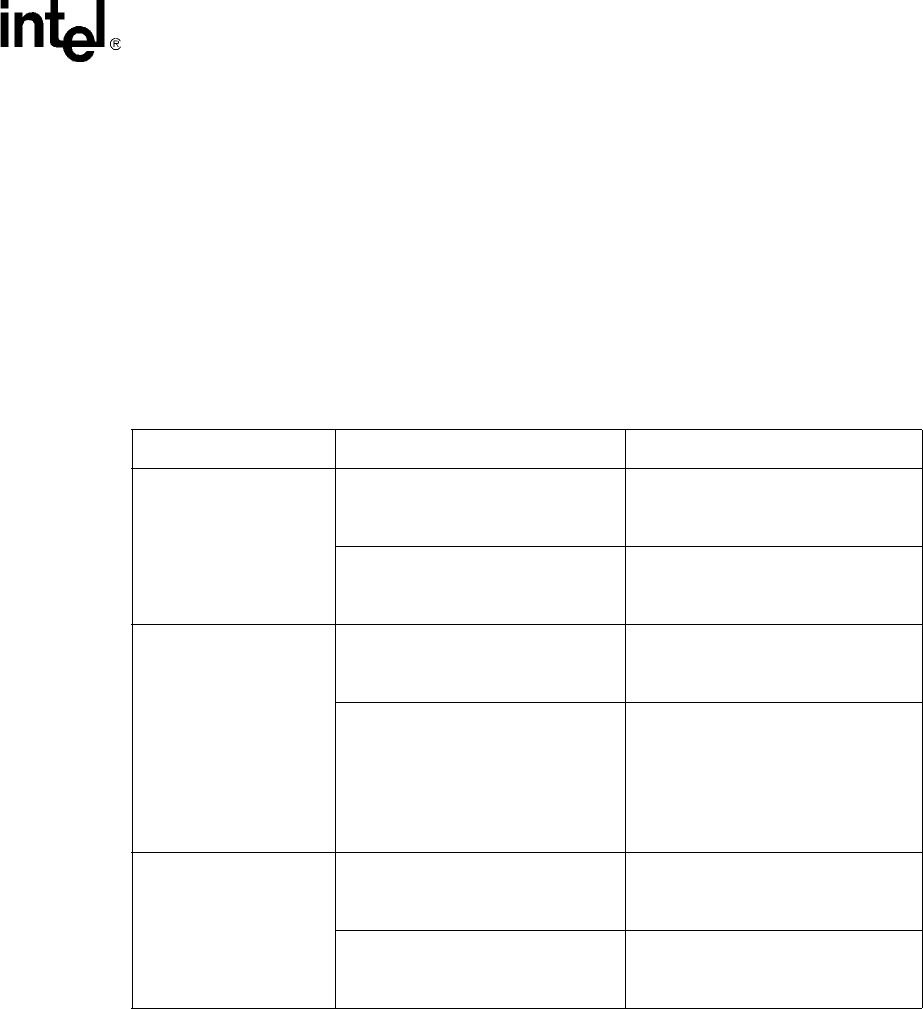

Table 81 shows the Intel XScale

®

core and Microengine instructions used to access devices on

these buses and it shows the buses that are used during the operation. For example, to read an APB

peripheral such as a UART CSR, a Microengine would execute a csr[read] instruction and the Intel

XScale

®

core would execute a Load (ld) instruction. Data is then moved between the CSR and the

Intel XScale

®

core/Microengine by first reading the CSR via the APB bus and then writing the

result to the Intel XScale

®

core/Microengine via the Push Bus.

7.1.2.3.4 Reset Registers

The reset registers reside in the SHaC. For more information on chip reset, refer to Section 10,

“Clocks and Reset”. Strapping pins are used to select the reset count (currently 140 cycles after

deassert). Options for reset count will be 64 (default), 128, 512, and 2048.

Table 81. Intel XScale

®

Core and Microengine Instructions

Accessing Read Operation Write Operation

APB Peripheral

Access Method:

Microengine: csr[read]

Intel XScale

®

core: ld

Access Method:

Microengine: csr[write]

Intel XScale

®

core: st

Bus Usages:

Read source: APB bus

Write dest: Push bus

Bus Usages:

Read source: Pull Bus

Write dest: APB bus

CAP CSR

Access Method:

Microengine: csr[read]

Intel XScale

®

core: ld

Access Method:

Microengine: csr[write], fast_wr

Intel XScale

®

core: st

Bus Usages:

Read source: CSR bus

Write dest: Push bus

Bus Usages:

csr[write] and st

Read source: Pull Bus

Write dest: CSR bus

fast_wr

Write dest: CSR bus

Microengine CSR or Xfer

register

(Reflector Mode)

Access Method:

Microengine: csr[read]

Intel XScale

®

core: ld

Access Method:

Microengine: csr[write]

Intel XScale

®

core: st

Bus Usages:

Read source: Pull bus (Address)

Write dest: Push bus(PP_ID)

Bus Usages:

Reads: Pull Bus (PP_ID)

Write dest: Push bus (Address)