Hardware Reference Manual 221

Intel

®

IXP2800 Network Processor

SRAM Interface

Other microcode rules:

• All access to atomic variables should be through read-modify-write instructions.

• If the flow must know that a write is completed (actually in the SRAM itself), follow the write

with a read to the same address. The write is guaranteed to be complete when the read data has

been returned to the Microengine.

• With the exception of initialization, never do write commands to the first three longwords of a

queue_descriptor data structure (these are the longwords that hold head, tail, and count).

All accesses to this data must be through the Q commands.

• To initialize the Q_array registers, perform a memory write of at least three longwords,

followed by a memory read to the same address (to guarantee that the write completed). Then,

for each entry in the

Q_array, perform a read_q_descriptor_head followed by a

read_q_descriptor_other using the address of the same three longwords.

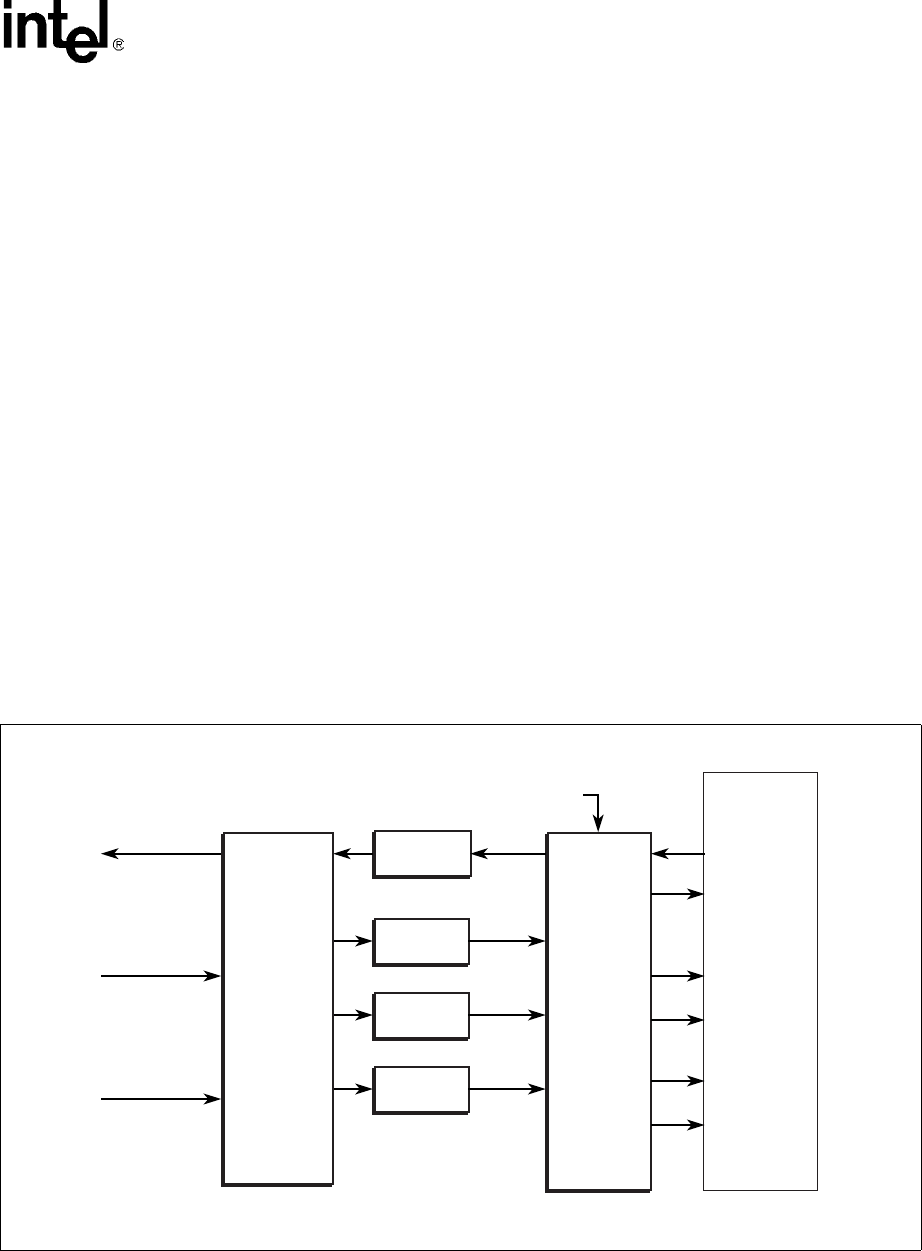

6.8 Coprocessor Mode

Each SRAM controller may interface to an external coprocessor through its standard QDR

interface. This interface allows for the cohabitation of both SRAM devices and coprocessors

operating on the same bus, and the coprocessor behaves as a memory-mapped device on the SRAM

bus. Figure 82 is a simplified block diagram of the SRAM controller. Figure 82 shows the

connection to a coprocessor through a standard QDR interface.

Note: Most coprocessors do not need a large number of address bits — connect as many bits of A

n as

required by the coprocessor.

Figure 82. Connection to a Coprocessor Though Standard QDR Interface

A9746-01

Push Data

FIFO

Read Cmd

FIFO

Write Cmd

FIFO

Pull Data

FIFO

Pin

Control

State

Mechanics

Coprocessor

Internal

Bus

Control

State

Mechanics

SRAM Push Bus

SRAM Cmd Bus

SRAM Pull Bus

SRAM_Control Coproessor

Qn[17:0]

Read

Data

Read

Address

Write

Address

Write

Data

RPE_Ln[1:0]

An[x:0]

BWEn[1:0]

WPE_Ln[1:0]

Dn[17:0]