332 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

PCI Unit

9.3 Slave Interface Block

The slave interface logic supports internal slave devices interfacing to the target port of the FBus.

• CSR — register access cycles to local CSRs.

• DRAM — memory access cycles to the DRAM push/pull Bus.

• SRAM — memory access cycles to the SRAM push/pull Bus.

The slave port of the FBus is connected to a 64-byte write buffer to support bursts of up to 64 bytes

to the memory interfaces. The slave read data are directly downloaded into the FBus read FIFO.

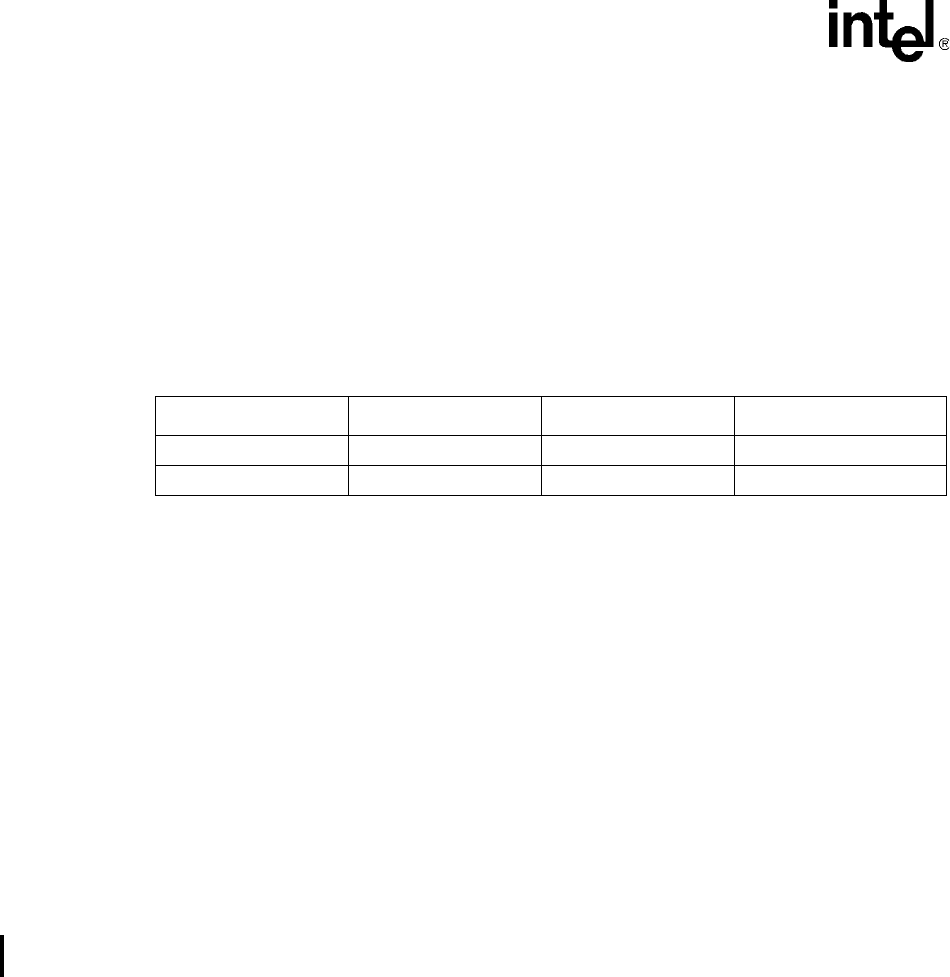

See Table 123.

As a push/pull command bus master, the PCI Unit translates these accesses into different types of

push/pull command. As the push/pull data bus target, the write data is sent through the pull data

bus and the read data is received on the push data bus.

9.3.1 CSR Interface

The internal Control and Status registers data is directed to or from the Slave FIFO port of the PCI

core FBus when the BAR id matches PCI_CSR_BAR (BAR0). The CSR accesses from the PCI

Bus directed towards CSRs not in PCI Unit is translated into a push/pull CSR type command. PCI

local CSRs are handled within the PCI Unit.

For writes, the data is sent when the pull bus is valid and the ID matches. The address is unloaded

from the FBus target address FIFO as indication to the PCI core logic that the cycle is completed.

The slave write buffer is not used for CSR access.

For reads, the data is loaded into the target receive FIFO as soon as the push bus is valid and the ID

matches. The address is unloaded from the FBus address FIFO.

Note: Target reads to the Scratch unit must always be in multiples of 32-bit (PCI_CBE_L[3:0] =0x0) as

the Scratch unit only supports 32-bit accesses.

One example of a PCI host access to internal registers is the initialization of internal registers and

memory to enable the Intel XScale

®

core to boot off the DRAM in the absence of a boot up PROM.

The accesses to the CSRs inside the PCI Unit are completed internally without sending the

transaction out to the push pull bus, just like the other internal register accesses.

Table 123. Slave Interface Buffer Sizes

Location Slave Address Slave Write Slave Read

Buffer Depth 1 64 Byte 0

Usage CSR, SRAM, DRAM SRAM, DRAM None