176 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Microengines

Example 25 shows another sequence of instructions and the value of the various operands.

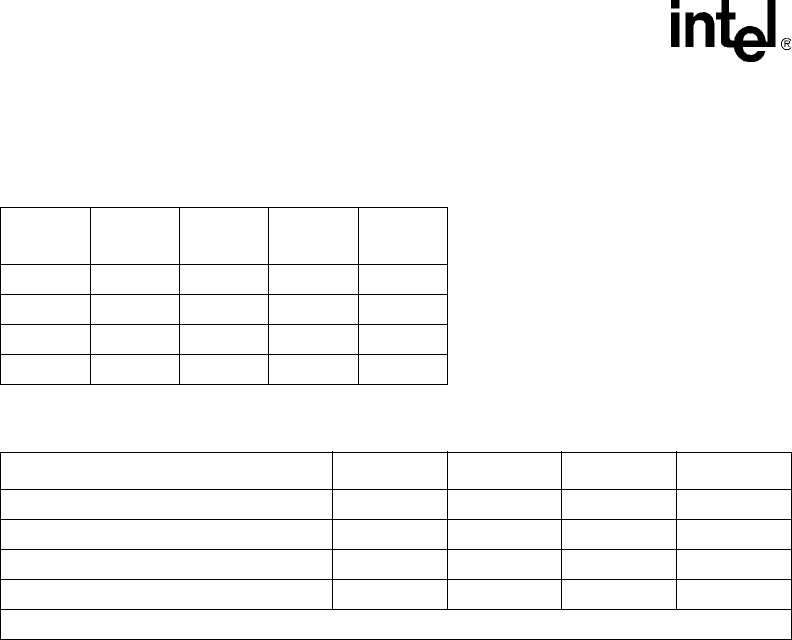

Table 60, shows the data in the registers for this example.

The value in Byte_Index[1:0] CSR (which controls the shift amount) for this example is 2.

As the examples show, byte aligning “n” words takes “n+1” cycles due to the first instruction

needed to start the operation.

Another mode of operation is to use the T_Index register with post-increment, to select the source

registers. T_Index operation is described later in this chapter.

4.3.2 CAM

The block diagram in Figure 59 is used to explain the CAM operation.

The CAM has 16 entries. Each entry stores a 32-bit value, which can be compared against a source

operand by instruction:

CAM_Lookup[dest_reg, source_reg].

All entries are compared in parallel, and the result of the lookup is a 9-bit value that is written into

the specified destination register in bits 11:3, with all other bits of the register set to 0 (the choice of

bits 11:3 is explained below). The result can also optionally be written into either of the LM_Addr

registers (see below in this section for details).

The 9-bit result consists of four State bits (dest_reg[11:8]), concatenated with a 1-bit Hit/Miss

indication (dest_reg[7]), concatenated with 4-bit entry number (dest_reg[6:3]). All other bits of

dest_reg are written with 0. Possible results of the lookup are:

• miss (0) — lookup value is not in CAM, entry number is Least Recently Used entry (which

can be used as a suggested entry to replace), and State bits are 0000.

• hit (1) — lookup value is in CAM, entry number is entry that has matched; State bits are the

value from the entry that has matched.

Table 60. Register Contents for Example 24

Register

Byte 3

[31:24]

Byte 2

[23:16]

Byte 1

[15:8]

Byte 0

[7:0]

03210

17654

2BA98

3FEDC

Example 25. Little-Endian Align

Instruction A Operand B Operand Prev A Result

Byte_align_le[--, r0] 3210 -- -- --

Byte_align_le[dest1, r1] 7654 3210 3210 5432

Byte_align_le[dest2, r2] BA98 7654 7654 9876

Byte_align_le[dest3, r3] FEDC BA98 BA98 DCBA

NOTE: B Operand comes from Prev_A register during byte_align_le instructions.