Hardware Reference Manual 37

Intel

®

IXP2800 Network Processor

Technical Description

The Microengine provides the following functionality during the Idle state:

1. The Microengine continuously checks if a Context is in Ready state. If so, a new Context

begins to execute. If no Context is Ready, the Microengine remains in the Idle state.

2. Only the ALU instructions are supported. They are used for debug via special hardware

defined in number 3 below.

3. A write to the USTORE_ADDR Local CSR with the USTORE_ADDR[ECS] bit set, causing

the Microengine to repeatedly execute the instruction pointed by the address specified in the

USTORE_ADDR CSR. Only the ALU instructions are supported in this mode. Also, the result

of the execution is written to the ALU_OUT Local CSR rather than a destination register.

4. A write to the USTORE_ADDR Local CSR with the USTORE_ADDR[ECS] bit set, followed

by a write to the USTORE_DATA Local CSR loads an instruction into the Control Store. After

the Control Store is loaded, execution proceeds as described in number 3 above.

2.3.4 Datapath Registers

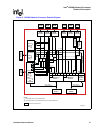

As shown in the block diagram in Figure 4, each Microengine contains four types of 32-bit

datapath registers:

1. 256 General Purpose registers

2. 512 Transfer registers

3. 128 Next Neighbor registers

4. 640 32-bit words of Local Memory

2.3.4.1 General-Purpose Registers (GPRs)

GPRs are used for general programming purposes. They are read and written exclusively under

program control. GPRs, when used as a source in an instruction, supply operands to the execution

datapath. When used as a destination in an instruction, they are written with the result of the

execution datapath. The specific GPRs selected are encoded in the instruction.

The GPRs are physically and logically contained in two banks, GPR A, and GPR B, defined in

Table 5.

2.3.4.2 Transfer Registers

Transfer (abbreviated as Xfer) registers are used for transferring data to and from the Microengine

and locations external to the Microengine, (for example DRAMs, SRAMs etc.). There are four

types of transfer registers.

• S_TRANSFER_IN

• S_TRANSFER_OUT

• D_TRANSFER_IN

• D_TRANSFER_OUT

TRANSFER_IN registers, when used as a source in an instruction, supply operands to the

execution datapath. The specific register selected is either encoded in the instruction, or selected

indirectly via T_INDEX. TRANSFER_IN registers are written by external units (A typical case is

when the external unit returns data in response to read instructions. However, there are other