Hardware Reference Manual 301

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

8.9.3 SPI-4.2 Support

Data is transferred across the SPI-4.2 interface in variously-sized bursts and encapsulated with a

leading and trailing control word. The control words provide annotation of the data with port

address (0-255) information, start-of-packet and end-of-packet markers, and an error detection

code (DIP-4). Data must be transferred in 16-byte integer multiples, except for the final burst of a

packet.

The status interface transfers state as an array of state or calendar, two bits per port, for all of the

supported ports. The status information provides for reporting one of three status states for each

port (satisfied, hungry, and starving) corresponding to credit availability for the port. The mapping

of calendar offset to port is flexible. Individual ports may be repeated multiple times for greater

frequency of update.

8.9.3.1 SPI-4.2 Receiver

The network processor receiver stores received SPI-4.2 bursts into receiver buffers. The buffers

may be configured as 128 buffers of 64 bytes, 64 buffers of 128 bytes, or 32 buffers of 256 bytes.

Information from the control words, the length of the burst, and the TCP checksum of the data are

stored in an additional eight bytes of control storage. The buffers support storage of bursts

containing an amount of data that is less than or equal to the buffer size. A burst that is greater than

the configured size of the buffers is stored in multiple buffers. Each buffer is made available to

software as it becomes filled.

As the filling of each buffer completes, the buffer is dispatched to a thread of a Microengine that

has been registered in a free list of threads, and the eight bytes of control information are forwarded

to the register context of the thread. If no thread is currently available, the receiver waits for a new

thread to become available as other buffers are also filled (and then also have “waiting queues”).

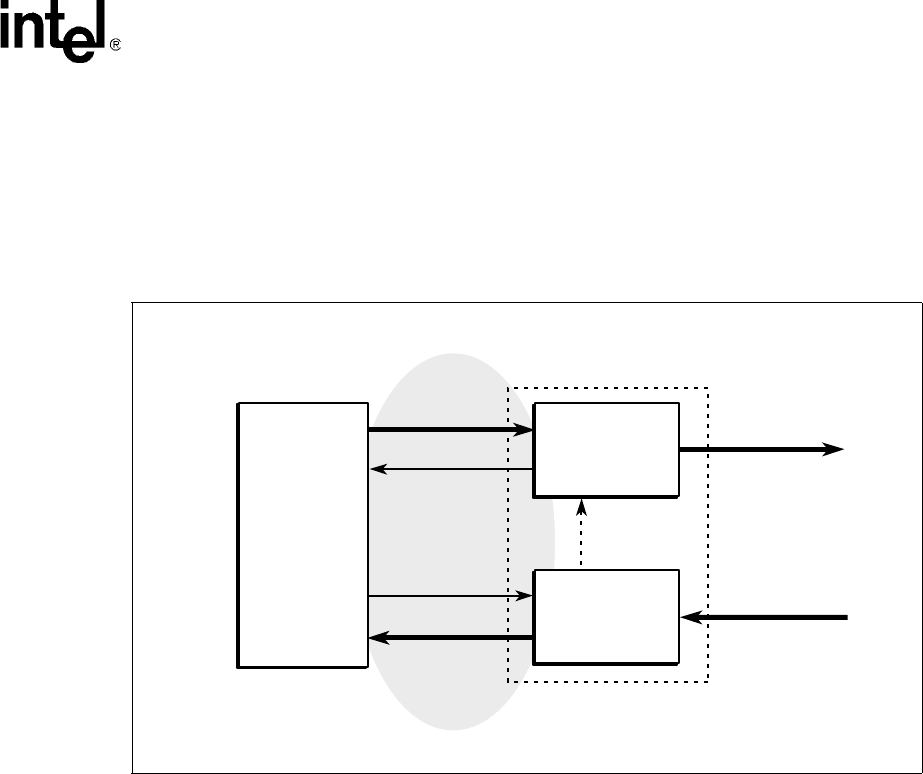

Figure 112. SPI-4.2 Interface Reference Model with Receiver and Transmitter Labels

Corresponding to Link Layer Device Functions

B2750-01

PHY

Device

Link

Layer

Device

Receiver

Signals

SPI-4.2

Interface

Transmitter

Signals

Ingress

Intel

®

IXP2800

Network

Processor

Egress

Intel IXP2800

Network

Processor