Hardware Reference Manual 35

Intel

®

IXP2800 Network Processor

Technical Description

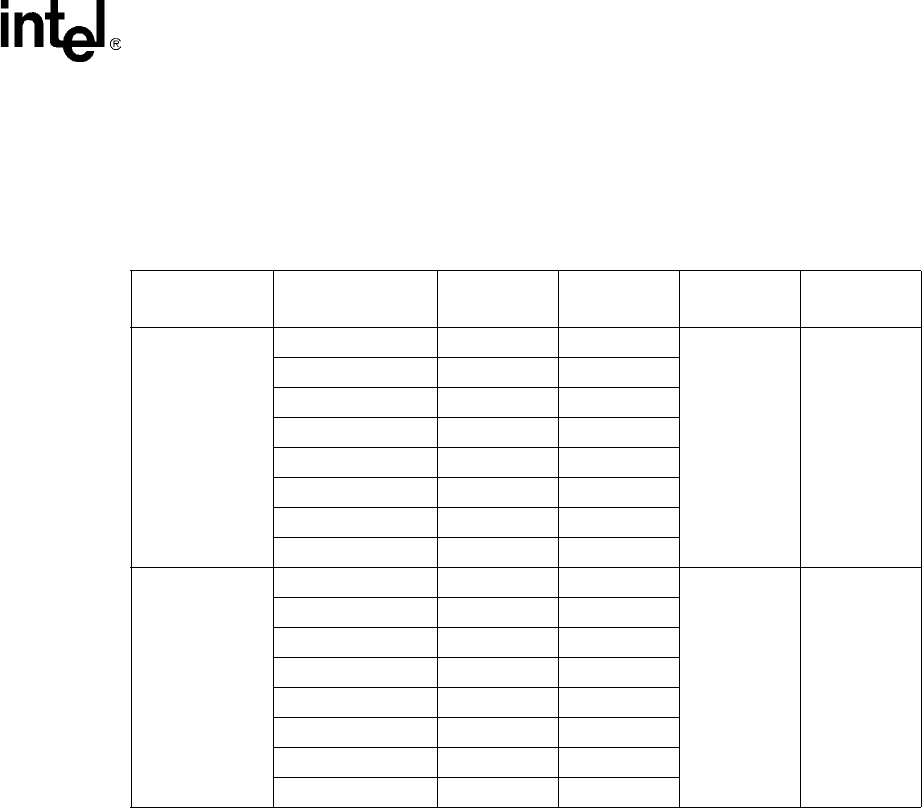

2.3.1 Microengine Bus Arrangement

The IXP2800 Network Processor supports a single D_Push/D_Pull bus, and both Microengine

clusters interface to the same bus. Also, it supports two command buses, and two sets of

S_Push/S_Pull buses connected as shown in Table 3, which also shows the next neighbor

relationship between the Microengine.

2.3.2 Control Store

The Control Store is a RAM that holds the program that is executed by the Microengine. It holds

8192 instructions, each of which is 40 bits wide. It is initialized by the Intel XScale

®

core, which

writes to USTORE_ADDR and USTORE_DATA Local CSRs.

The Control Store is protected by parity against soft errors. Parity checking is enabled by

CTX_ENABLE[CONTROL STORE PARITY ENABLE]. A parity error on an instruction read

will halt the Microengine and assert an interrupt to the Intel XScale

®

core.

2.3.3 Contexts

There are eight hardware Contexts available in the Microengine. To allow for efficient context

swapping, each Context has its own register set, Program Counter, and Context specific Local

registers. Having a copy per Context eliminates the need to move Context specific information to/

from shared memory and Microengine registers for each Context swap. Fast context swapping

allows a Context to do computation while other Contexts wait for I/O (typically external memory

accesses) to complete or for a signal from another Context or hardware unit. (A context swap is

similar to a taken branch in timing.)

Table 3. IXP2800 Network Processor Microengine Bus Arrangement

Microengine

Cluster

Microengine

Number

Next

Neighbor

Previous

Neighbor

Command

Bus

S_Push and

S_Pull Bus

0

0x00 0x01 NA

0 0

0x01 0x02 0x00

0x02 0x03 0x01

0x03 0x04 0x02

0x04 0x05 0x03

0x05 0x06 0x04

0x06 0x07 0x05

0x07 0x10 0x06

1

0x10 0x11 0x07

11

0x11 0x12 0x10

0x12 0x13 0x11

0x13 0x14 0x12

0x14 0x15 0x13

0x15 0x16 0x14

0x16 0x17 0x15

0x17 NA 0x16