Hardware Reference Manual 389

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

11.4.6 External Input Events

11.4.6.1 XPI Events Target ID(000001) / Design Block #(0100)

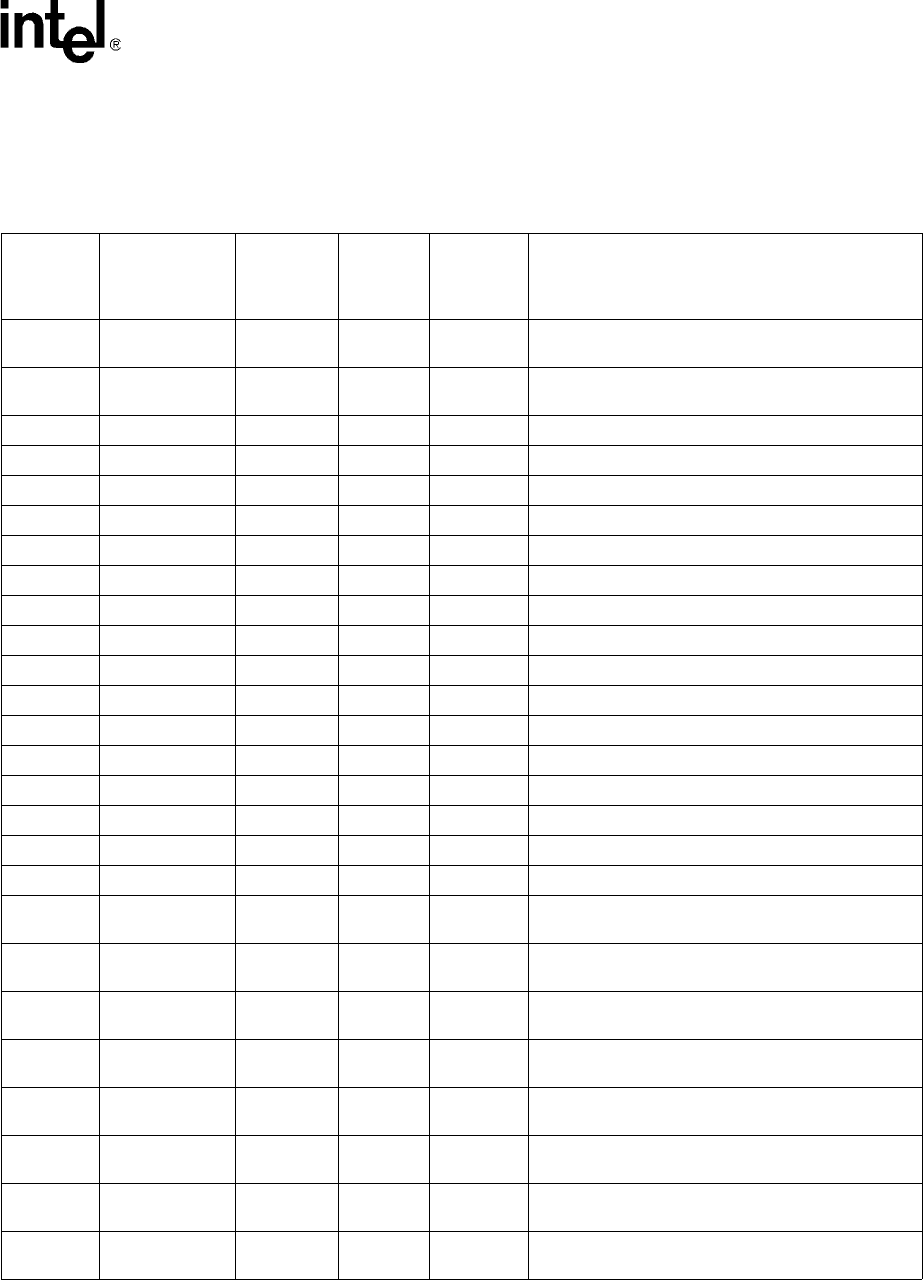

Table 155. XPI PMU Event List (Sheet 1 of 4)

Event

Number

Event Name

Clock

Domain

Single

pulse/

Long

pulse

Burst Description

0 XPI_RD_P APB_CLK single separate

It includes all the read accesses, PMU, timer, GPIO,

UART, and Slowport.

1 XPI_WR_P APB_CLK single separate

It includes all the write accesses, PMU, timer, GPIO,

UART, and Slowport.

2 PMU_RD_P APB_CLK single separate It executes the read access to the PMU unit.

3 PMU_WR_P APB_CLK single separate It executes the write access to the PMU unit.

4 UART_RD_P APB_CLK single separate It executes the read access to the UART unit.

5 UART_WR_P APB_CLK single separate It executes the write access to the UART unit.

6 GPIO_RD_P APB_CLK single separate It executes the read access to the GPIO unit.

7 GPIO_WR_P APB_CLK single separate It executes the write access to the GPIO unit.

8 TIMER_RD_P APB_CLK single separate It executes the read access to the Timer unit.

9 TIMER_WR_P APB_CLK single separate It executes the write access to the Timer unit.

10 SPDEV_RD_P APB_CLK single separate It executes the read access to the Slowport Device.

11 SPDEV_WR_P APB_CLK single separate It executes the write access to the Slowport Device.

12 SPCSR_RD_P APB_CLK single separate It executes the read access to the Slowport CSR.

13 SPCSR_WR_P APB_CLK single separate It executes the write access to the Slowport CSR.

14 TM0_UF_P APB_CLK single separate It shows the occurrence of timer 1 counter underflow.

15 TM1_UF_P APB_CLK single separate It shows the occurrence of timer 2 counter underflow.

16 TM2_UF_P APB_CLK single separate It shows the occurrence of timer 3 counter underflow.

17 TM3_UF_P APB_CLK single separate It shows the occurrence of timer 4 counter underflow.

18 IDLE0_0_P APB_CLK single separate

It displays the idle state of the state machine 0 for the

mode 0 of Slowport.

19 START0_1_P APB_CLK single separate

It enters the start state of the state machine 0 for the

mode 0 of Slowport.

20 ADDR10_3_P APB_CLK single separate

It enters the first address state, AD[9:2], of the state

machine 0 for the mode 0 of Slowport.

21 ADDR20_2_P APB_CLK single separate

It enters the second address state, AD[17:10], of the

state machine 0 for the mode 0 of Slowport.

22 ADDR30_6_P APB_CLK single separate

It enters the third address state, AD[24:18], of the

state machine 0 for the mode 0 of Slowport.

23 SETUP0_4_P APB_CLK single separate

It enters data setup state of the state machine 0 for

the mode 0 of Slowport.

24 PULW0_5_P APB_CLK single separate

It enters data duration state of the state machine 0 for

the mode 0 of Slowport.

25 HOLD0_D_P APB_CLK single separate

It enters data hold state of the state machine 0 for the

mode 0 of Slowport.