306 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

The backpressure signal (TXCFC, RXCFC) is an asynchronous signal and is asserted by the

ingress network processor to prevent overflow of the ingress network processor ingress flow

control FIFO. If the egress network processor is so optionally configured, it will react to assertion

of the backpressure signal for 32 clock cycles (64 edges) as a request for a de-skew training

sequence to be transmitted on the flow control interface.

The flow control interface only supports a 32-bit CWord. Flow Control CFrames that are received

by the egress network processor are stripped of any padding associated with large CWord widths

and forwarded to the flow control interface.

The various options for parity calculation and checking supported on the data interface are

supported on the flow control interface. Horizontal parity checking may be optionally disabled.

The standard calculation of vertical parity may be replaced with a DIP-16 calculation.

8.9.4.2.3

Support for Simplex Operation

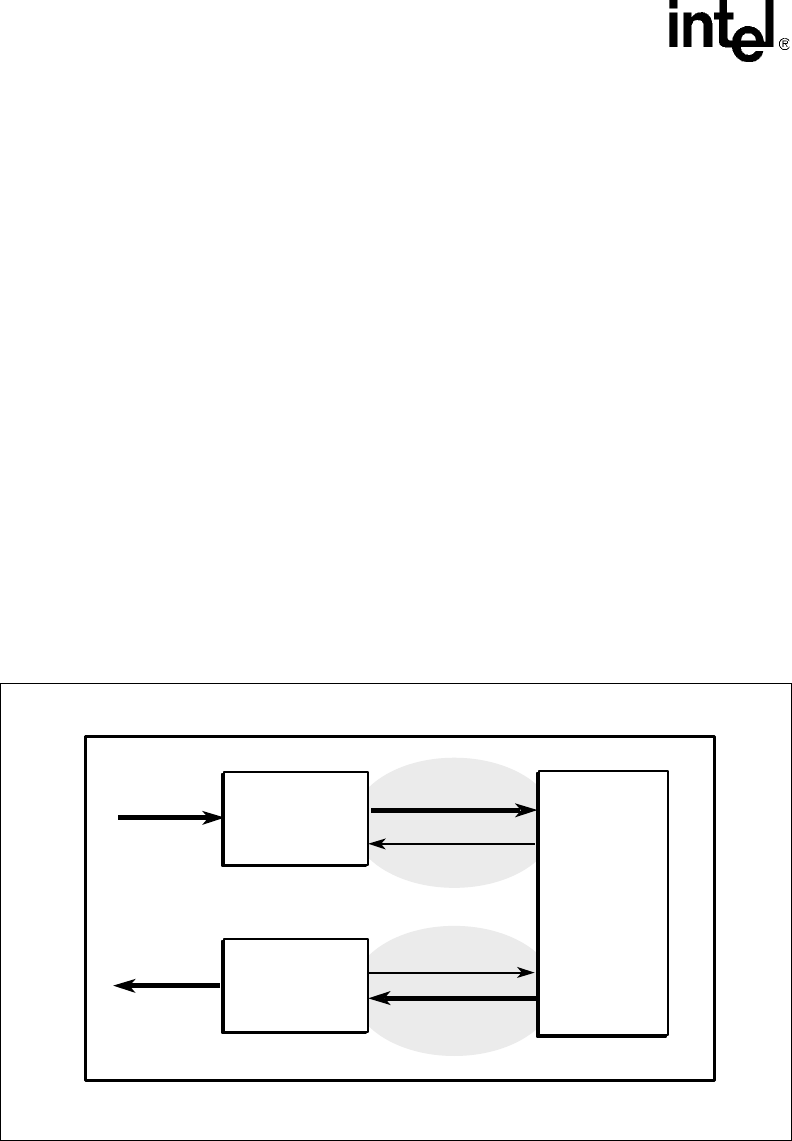

The network processor supports a mode of operation that supports the CSIX-L1 protocol, but offers

an independent interface for the ingress and egress network processors. In this mode, the ingress

and egress network processors each offer an independent full-duplex CSIX-L1 flavor of interface

to the fabric, but the network processor-to-fabric interface on the egress network processor and the

fabric-to-network processor interface of the ingress network processor are of reduced width,

consisting of four (instead of 16) data signals. These narrow interfaces are referred to as Reverse

Path Control Interfaces and use the same physical interface as the flow control interface in the

dual-chip, full duplex configuration. They support the transfer of Flow Control CFrames and the

CRdy and DRdy “ready” bits, but are not intended to support the transfer of data CFrames.

The Reverse Path Control Interfaces (RPCI) support only the 32-bit CWord width of the dual chip,

full duplex flow control interface. The variations of parity support provided by the data interface

and the flow control interface are supported by the RPCI.

Figure 114. Reference Model for IXP2800 Support of the Simplex Configuration Using

Independent Ingress and Egress Interfaces

B2752-01

Primary

Interface

RPCI

Fabric

Interface

Chip(s)

Primary

Interface

RPCI

Ingress

Network

Processor

Egress

Network

Processor

Printed Circuit Card