Hardware Reference Manual 201

Intel

®

IXP2800 Network Processor

DRAM

5.10.6 Arbitration

The channel needs to arbitrate among several different operations at RMC. Arbitration rules are

given here for those cases: from highest to lowest priority:

• Refresh RDRAM.

• Current calibrate RDRAM.

• Bank operations. When there are multiple bank operations ready, the rules are: (1) round robin

among banks to avoid bank collisions, and (2) skip a bank to avoid DQ bus turnarounds. No

bank can be skipped more than twice.

Commands are given to RMC in the order in which they will be executed.

5.10.7 Reference Ordering

Table 67 lists the ordering of reads and writes to the same address for DRAM. The definition of

first and second is defined by the time the command is valid on the command bus.

5.11 DRAM Push/Pull Arbiter

The DRAM Push/Pull Arbiter contains the push and pull arbiters for the D-Cluster (DRAM

Cluster). Both the PUSH and PULL data buses have multiple masters and multiple targets. The

DRAM Push/Pull Arbiter determines which master gets to drive the data bus for a given

transaction and makes sure that the data is delivered correctly.

This unit has the following features:

• Up to three DX Unit (DRAM Unit) masters.

• 64-bit wide push and pull data buses.

• Round-robin arbitration scheme.

• Peak delivery of 64 bits per cycle.

• Supports third-party data transfers; the Microengine’s can command data movements between

the MSF (Media) and either the DX Units or the CR Units.

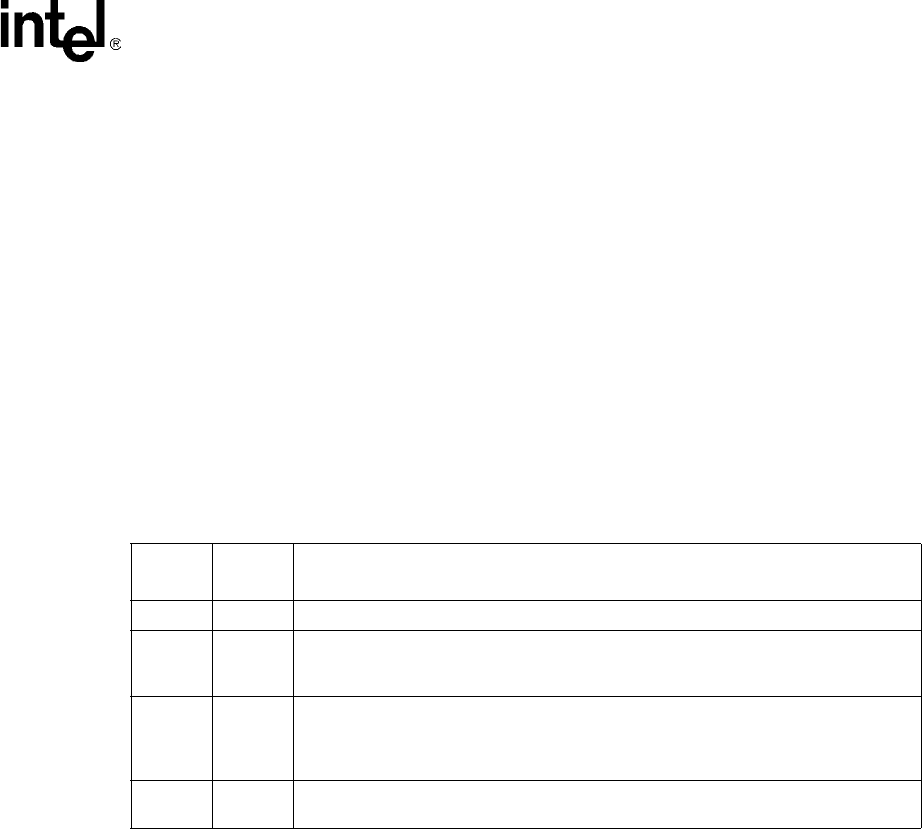

Table 67. Ordering of Reads and Writes to the Same Address for DRAM

First

Access

Second

Access

Ordering Rules

Read Read None. If there are no side-effects on reads, both readers get the same data.

Read Write

Reader must get the pre-modified data. This is not enforced in hardware. The write

instruction must not be executed until after the Microengine receives the signal of read

completion (i.e., program must use sig_done on the read).

Write Read

Reader must get the post-modified data. This is not enforced in hardware. The read

instruction must not be executed until after the Microengine receives the signal of write

completion (i.e., program must use

sig_done token on the write instruction and wait

for the signal before executing the read instruction).

Write Write

The hardware guarantees that the writes complete in the order in which they are

issued.