Hardware Reference Manual 237

Intel

®

IXP2800 Network Processor

SHaC — Unit Expansion

7.1.3.1 Hashing Operation

Up to three hash indexes (see Example 33) can be created by using one Microengine instruction.

A Microengine initiates a hash operation by writing a contiguous set of SRAM Transfer registers

and then executing the hash instruction. The SRAM Transfer registers can be specified as either

Context-Relative or Indirect; Indirect allows any of the SRAM Transfer registers to be used. Two

SRAM Transfer registers are required to create hash indexes for 48-bit and 64-bit, and four SRAM

Transfer registers to create 128-bit hash indexes, as shown in Table 82. In the case of the 48-bit

hash, the Hash Unit ignores the upper two bytes of the second Transfer register.

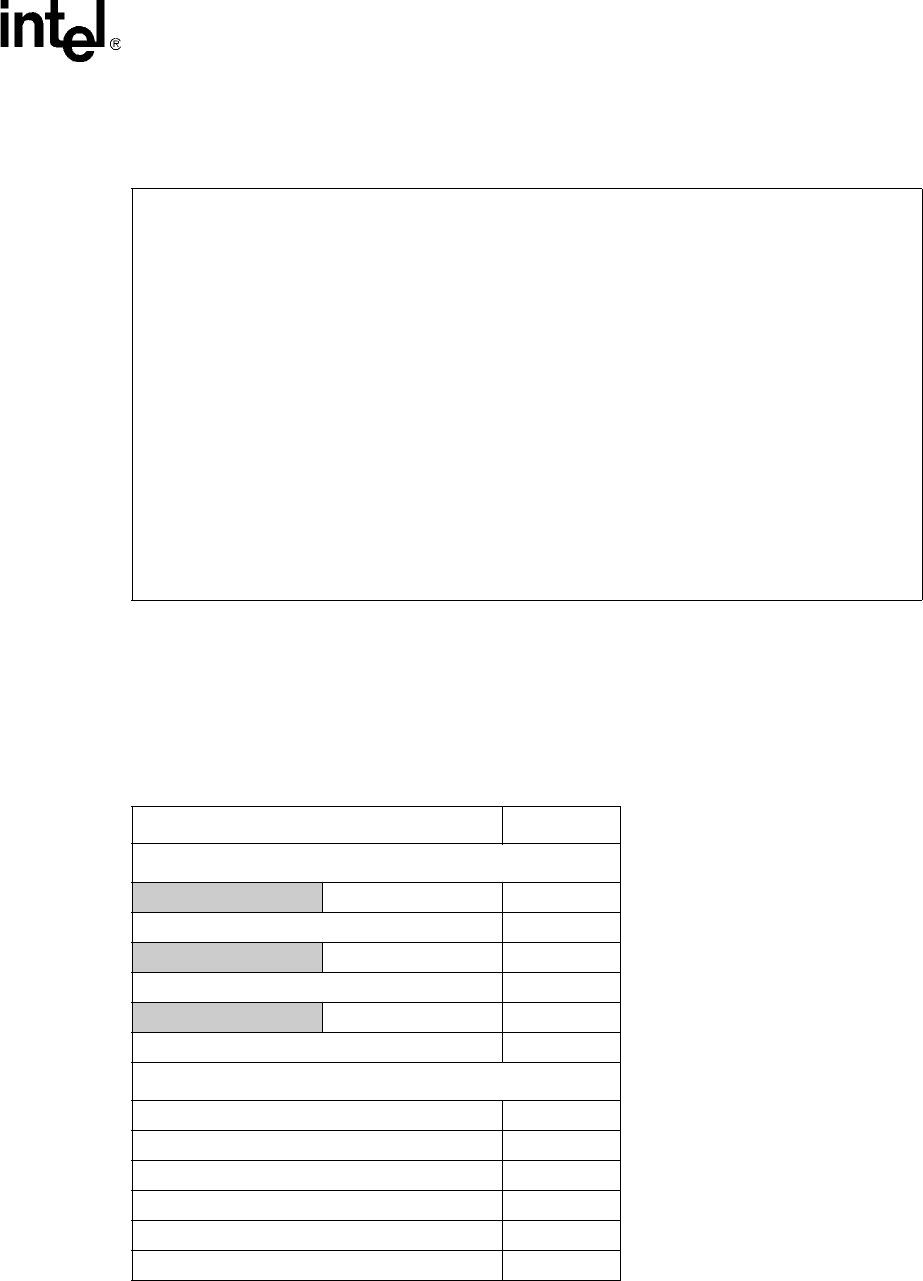

Example 33. Microengine Hash Instructions

hash1_48[$xfer], optional_token

hash2_48[$xfer], optional_token

hash3_48[$xfer], optional_token

hash1_64[$xfer], optional_token

hash2_64[$xfer], optional_token

hash3_64[$xfer], optional_token

hash1_128[$xfer], optional_token

hash2_128[$xfer], optional_token

hash3_128[$xfer], optional_token

Where:

$xfer

The beginning of a contiguous set of registers that supply the data used

to create the hash input and receive the hash index upon completion of

the hash operation.

optional_token sig_done, ctx_swap, defer [1]

Table 82. S_Transfer Registers Hash Operands (Sheet 1 of 2)

Register Address

48-Bit Hash Operations

Don't care hash 3[47:32] $xfer n+5

hash 3 [31:0] $xfer n+4

Don't care hash 2[47:32] $xfer n+3

hash 2 [31:0] $xfer n+2

Don't care hash 1[47:32] $xfer n+1

hash 1 [31:0] $xfer n

64-Bit Hash Operations

hash 3 [63:32] $xfer n+5

hash 3 [31:0] $xfer n+4

hash 2 [63:32] $xfer n+3

hash 2 [31:0] $xfer n+2

hash 1 [63:32] $xfer n+1

hash 1 [31:0] $xfer n