Hardware Reference Manual 347

Intel

®

IXP2800 Network Processor

PCI Unit

9.4.2.3.2 PCI Address Generation for Configuration Cycles

When a push/pull command bus master is accessing the PCI Bus to generate a configuration cycle,

the PCI address is generated based on the a Command Bus Master address as shown in Table 128

and Figure 129:

9.4.2.3.3 PCI Address Generation for Special and IACK Cycles

The PCI address is undefined for special and IACK PCI cycles.

9.4.2.3.4 PCI Enables

The PCI byte-enables are generated based on the Command Bus Master instruction, and the PCI

unit does not change the states of the enables.

9.4.2.3.5 PCI Command

The PCI command is derived from the Command Bus Master address space map. The different

spaces supported are listed in Table 129:

Table 128. Command Bus Master Configuration Transactions

Cycle Result

Type 1 Configuration Cycle Command Bus address bits [31:24] are equal to 0xDA

Type 0 Configuration Cycle Command Bus address bits [31:24] are equal to 0xDB.

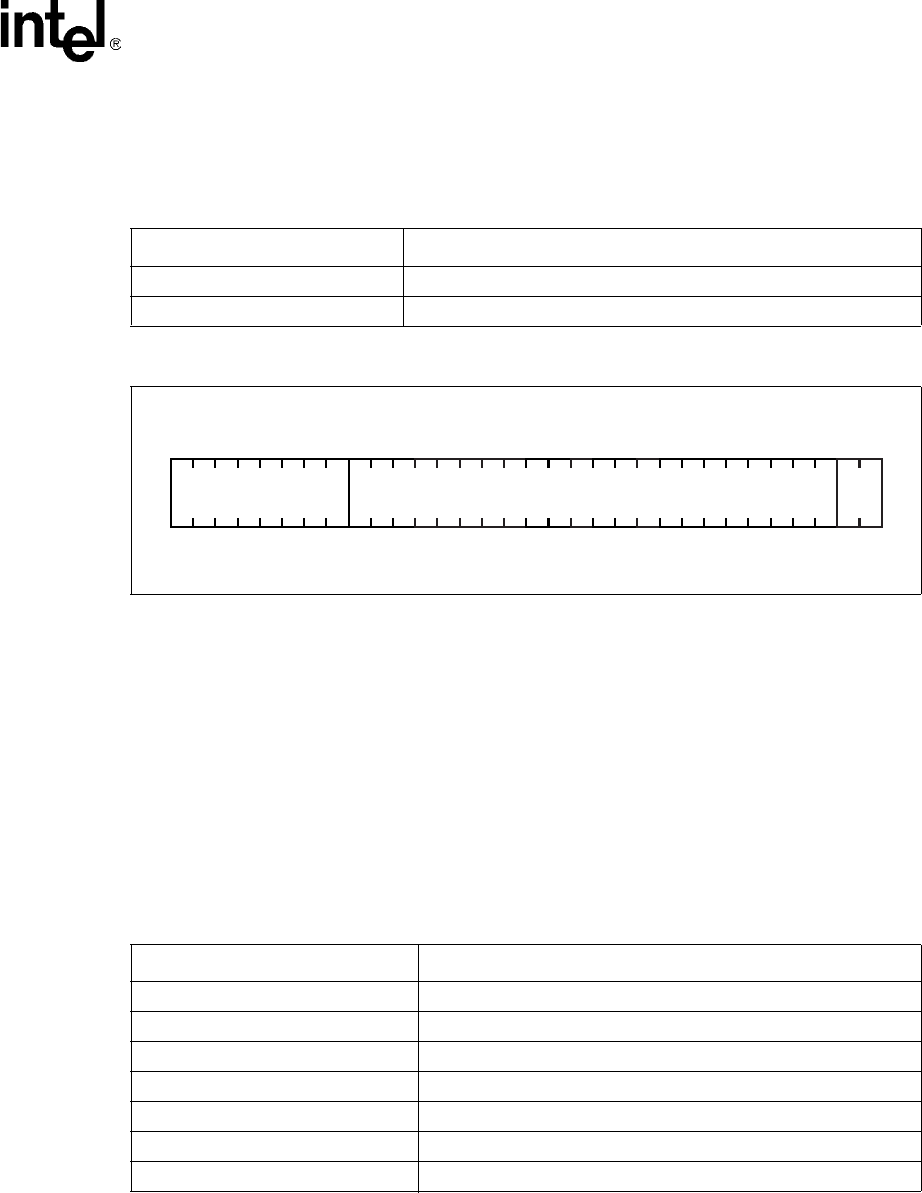

Figure 129. PCI Address Generation for Command Bus Master to PCI Configuration Cycle

A9776-02

31 2627282930 232425 19202122 15161718 1214 13 891011 45673210

0000 0000

00

Intel XScale

®

Core Address[23:2]

Table 129. Command Bus Master Address Space Map to PCI

PCI Command Intel XScale

®

Core Address Space

PCI Memory 0xE000 0000 – 0xFFFF FFFF

Local CSR 0xDF00 0000 – 0xDFFF FFFF

Local Configuration Register 0xDE00 0000 – 0xDEFF FFFF

PCI Special Cycle/PCI IACK Read 0xDC00 0000 – 0xDDFF FFFF

PCI Type 1 Configuration Cycle 0xDB00 0000 – 0xDBFF FFFF

PCI Type 0 Configuration Cycle 0xDA00 0000 – 0xDAFF FFFF

PCI I/O 0xD800 0000 – 0xD8FF FFFF