258 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

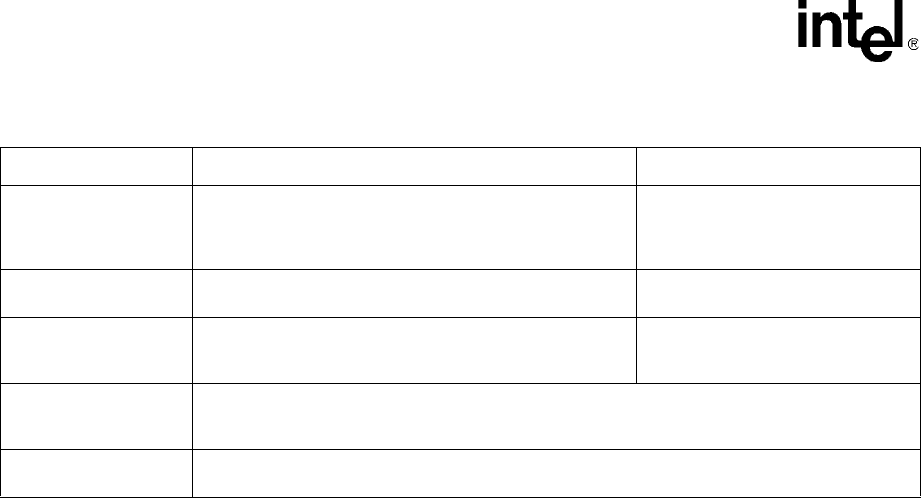

Table 93 summarizes the differences in RBUF operation between the SPI-4 and CSIX protocols.

8.2.7 Receive Flow Control Status

Flow control is handled in hardware. There are specific functions for SPI-4 and CSIX.

8.2.7.1 SPI-4

SPI-4, FIFO status information is sent periodically over the RSTAT signals from the Link Layer

device (which is the IXP2800 Network Processor) to the PHY device. (Note that TXCDAT pins

can act as RSTAT based on the MSF_Rx_Control[RSTAT_Select] bit.) The information to be sent

is based on the number of RBUF elements available to receive SPI-4.

The FIFO status of each port is encoded in a 2-bit data structure — code 0x3 is used for framing the

data, and the other three codes are valid status values. The FIFO status words are sent according to

a repeating calendar sequence. Each sequence begins with the framing code to indicate the start of

a sequence, followed by the status codes, followed by a parity code covering the preceding frame.

The length of the calendar is defined in Rx_Calendar_Length, which is a CSR field that is

initialized with the length of the calendar, since in many cases fewer than 256 ports are in use.

When TRAIN_DATA[RSTAT_En] is disabled, RSTAT is held at 0x3.

The IXP2800 Network Processor transmits FIFO status only if TRAIN_DATA[RSTAT_En] is

set. The logic sends “Satisfied,” Hungry,” or “Starving” based on either the upper limit of the

RBUF, a global override value set in MSF_Rx_Control[RSTAT_OV_VALUE], or a port-specific

override value set in RX_PORT_CALENDAR_STATUS_#. The choice is controlled by

MSF_RX_CONTROL[RX_Calendar_Mode].

When set to Conservative_Value, the status value sent for each port is the most conservative of:

• The RBUF upper limit

• MSF_RX_CONTROL[RSTAT_OV_VALUE]

• RX_PORT_CALENDAR_STATUS_#

“Satisfied” is more conservative than “Hungry,” which is more conservative than “Starving.”

Table 93. Summary of SPI-4 and CSIX RBUF Operations

Operation SPI-4 CSIX

When is RBUF Element

Allocated?

Upon receipt of Payload Control Word or when Element data

section fills and more Data Words arrive. The Payload

Control Word allocates an element for data that will be

received subsequent to it.

Start of Frame and Base Header Type

is mapped to RBUF (in the

CSIX_Type_Map CSR).

How Much Data is Put

into Element?

All Data Words received between two Payload Control

Words, or number of bytes in the element, whichever is less.

Number of bytes specified in Payload

Length field of Base Header.

How is RBUF Element

Set Valid?

Upon receipt of Payload Control Word or when Element data

section fills. The Payload Control Word validates the element

holding data received prior to it.

All Payload is received (or if

premature SOF, which will set an

error bit in Element Status).

How is RBUF Element

Handed to Microengine?

Element Status is pushed to Microengine at the head of the appropriate Rx_Thread_Freelist_#

(based on the protocol). Status is pushed to two consecutive Transfer registers; bits[31:0] of Element

Status to the first Transfer register and bits[63:32] to the next higher numbered Transfer register.

How is RBUF Element

returned to free list?

CSR write to RBUF_Element_Done.