Hardware Reference Manual 331

Intel

®

IXP2800 Network Processor

PCI Unit

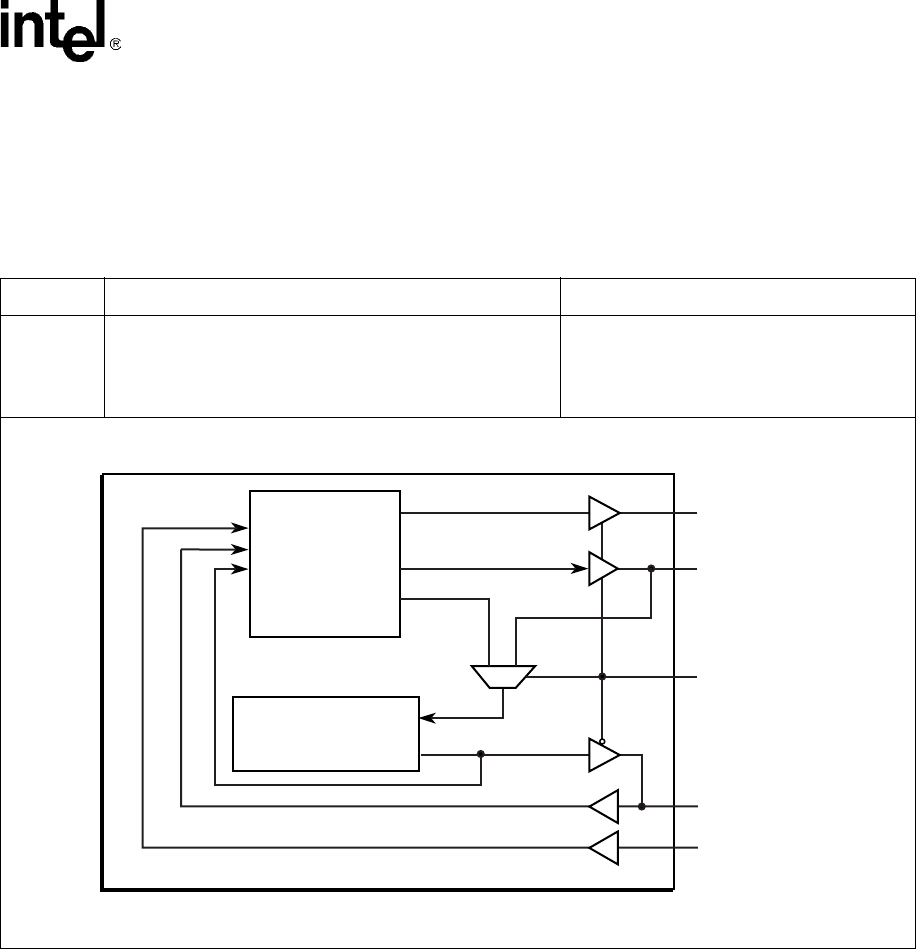

9.2.11.3 PCI Internal Arbiter

The PCI unit contains a PCI bus arbiter that supports two external masters in addition to the PCI

Unit’s initiator interface. To enable the PCI arbiter, the CFG_PCI_ARB(GPIO[2]) strapping pin

must be 1 during reset. As shown in Figure 120, the local bus request and grant pair become

externally not visible. These signals will be made available to external debug pins for debug

purpose.

The arbiter uses a simple round-robin priority algorithm, The arbiter asserts the grant signal

corresponding to the next request in the round-robin during the current executing transaction on the

PCI bus (this is also called hidden arbitration). If the arbiter detects that an initiator has failed to

assert frame_l after 16 cycles of both grant assertion and PCI bus idle condition, the arbiter de-

asserts the grant. That master does not receive any more grants until it de-asserts its request for at

least one PCI clock cycle. Bus parking is implemented in that the last bus grant will stay asserted if

no request is pending.

To prevent bus contention, if the PCI bus is idle, the arbiter never asserts one grant signal in the

same PCI cycle in which it de-asserts another. It de-asserts one grant, and then asserts the next

grant after one full PCI clock cycle has elapsed to provide for bus driver turnaround.

Figure 120. PCI Arbiter Configuration Using CFG_PCI_ARB(GPIO[2])

Pin CFG_PCI_ARB(GPIO[2]) = 0 (during reset) CFG_PCI_ARB(GPIO[2]) = 1(during reset)

GNT_L[0]

GNT_L[1]

REQ_L[0]

REQ_L[1]

PCI Bus Grant Input to IXP2800 Network Processor

Not Used, Float

PCI Bus Request Output from IXP2800 Network Processor

Not Used, Tied High

PCI Bus Grant Output to Master 1

PCI Bus Grant Output to Master 2

PCI Bus Request Input from Master 1

PCI Bus Request Input from Master 1

A9767-03

PCI Master

State Machine

PCI Arbiter

GNT_L

GNT_L[2:0]

REQ_L[2:0]

GNT_L[1]

GNT_L[0]

CFG_PCI_ARB

REQ_L[0]

REQ_L[1]

REQ_L

PCI UNIT

0

1