Hardware Reference Manual 185

Intel

®

IXP2800 Network Processor

Microengines

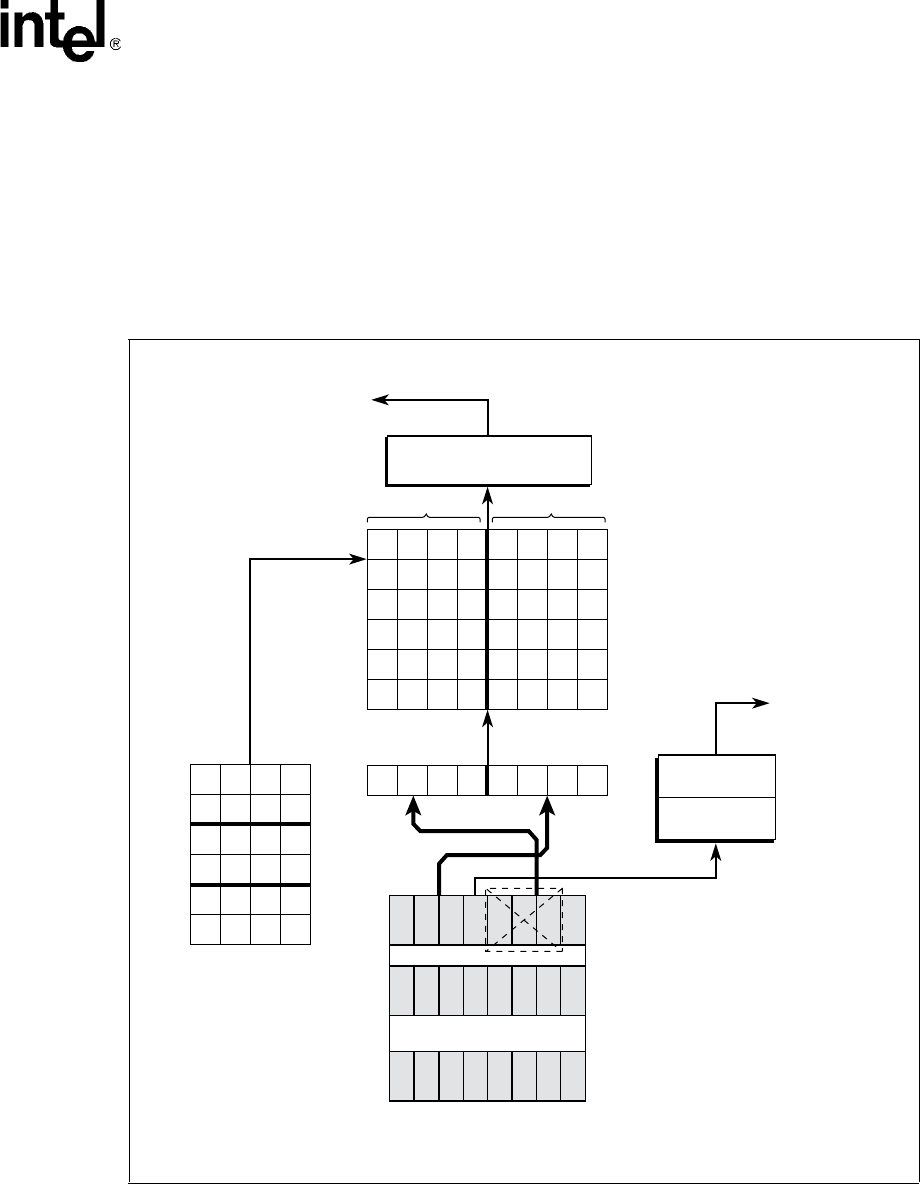

4.5.2.2 Write to TBUF

For writing to TBUF, the header comes from the Microengine and data comes from RBUF or

DRAM. Since the Microengine to TBUF header transfer happened in 8-byte chunks, it is possible

that the first longword that is inside tr0 may not contain any data if the valid header begins in

transfer register tr1. Since data in tr0 goes to the LW1 location at offset 0 and data in tr2 goes to the

LW0 location at offset 0, there are some invalid bytes at the beginning of the header, at offset 0.

These invalid bytes are removed by the aligner on the way out of TBUF, based on the control word

for this TBUF element. The data from tr2, tr3, ... tr6 is placed in TBUF, as shown in Figure 64 in

big-endian order.

Figure 64. Write to TBUF

A8945-01

RBUF or DRAM

MicroEngine

Transfer Registers

To SPI-4

64-bit Read

from addr 1 by

MicroEngine

addr 0000_0000

offset 0

offset 1

offset 2

offset 3

offset 4

offset 5

addr 0001_0000

A63 addr0

tr0

tr1

tr2

tr3

tr4

tr5

LW0

4

XXX34567

5670123

12 13 14 15 8 9 10 11

20 21 22 23 16 17 18 19

treg 0 gets

0123

Remove the empty bytes

based on the control word

treg 1 gets

4567

LW1

XXXX

X h1h2h3

h4 h5 h6 h7

h8 h9 h10 h11

h12 h13 X X

XXXX

XXXXXh1h2h3

h4 h5 h6 h7 h8 h9 h10 h11

h12h13XXXXXX

XXX34567

8 9 10 11 12 13 14 15

16 17 18 19 20 21 22 23