Hardware Reference Manual 391

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

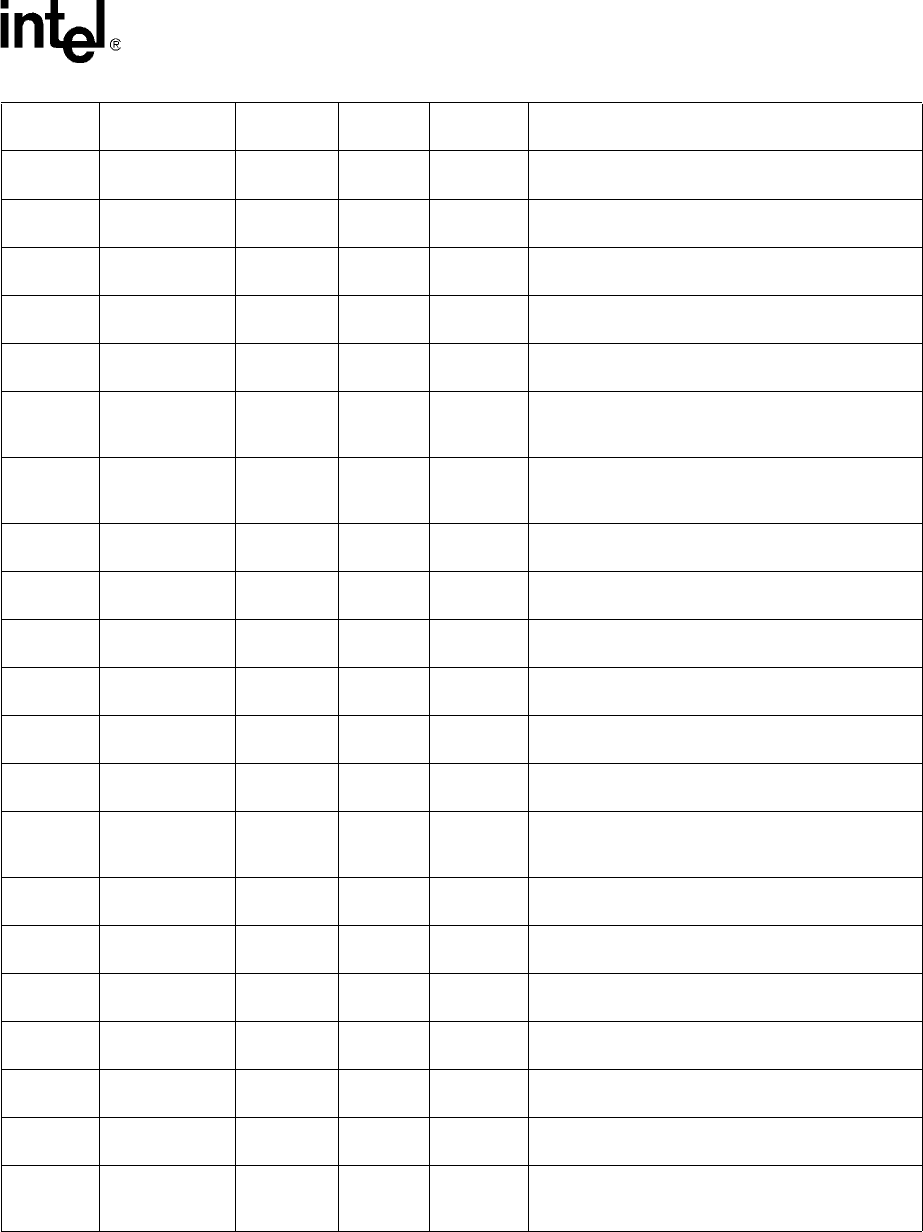

48 SETUP2_4_P APB_CLK single separate

It enters the pulse width of the data transaction cycle

for the state machine 2 for the mode 2 of Slowport.

49 PULW2_C_P APB_CLK single separate

It enters the pulse width of the data transaction cycle

for the state machine 2 for the mode 2 of Slowport.

50 HOLD2_E_P APB_CLK single separate

It enters the data hold period for the state machine 2

for the mode 2 of Slowport.

51 OUTEN2_F_P APB_CLK single separate

It starts to assert the OE when the state machine 2 is

active for the mode 2 of Slowport.

52 PKDATA2_D_P APB_CLK single separate

It enters the read data packing state during the active

state machine 2 for the mode 2 of Slowport.

53 LADATA2_9_P APB_CLK single separate

It enters the data capturing cycle during the active

state machine 2 for the mode 2 of Slowport.

54 READY2_B_P APB_CLK single separate

It enters the acknowledge state to terminate the read

cycle when the state machine 2 is active for the mode

2 of Slowport.

55 TURNA2_8_P APB_CLK single separate

It enters the turnaround state of the transaction when

the state machine 2 is active for the mode 2 of

Slowport.

56 IDLE3_0_P APB_CLK single separate

It displays the idle state of the state machine 3 for the

mode 3 of Slowport.

57 START3_1_P APB_CLK single separate

It enters the start state of the state machine 3 for the

mode 3 of Slowport.

58 ADDR13_3_P APB_CLK single separate

It enters the first address state, AD[7:0], of the state

machine 3 for the mode 3 of Slowport.

59 ADDR23_2_P APB_CLK single separate

It enters the second address state, AD[15:8], of the

state machine 3 for the mode 3 of Slowport.

60 ADDR33_6_P APB_CLK single separate

It enters the second address state, AD[23:16], of the

state machine 3 for the mode 3 of Slowport.

61 ADDR43_7_P APB_CLK single separate

It enters the second address state, AD[24], of the

state machine 3 for the mode 3 of Slowport.

62 WRDATA3_5_P APB_CLK single separate

It unpacks the data from the APB onto the Slowport

bus for the state machine 3 for the mode 3 of

Slowport.

63 SETUP3_4_P APB_CLK single separate

It enters the pulse width of the data transaction cycle

for the state machine 3 for the mode 3 of Slowport.

64 PULW3_C_P APB_CLK single separate

It enters the pulse width of the data transaction cycle

for the state machine 3 for the mode 3 of Slowport.

65 HOLD3_E_P APB_CLK single separate

It enters the data hold period for the state machine 3

for the mode 3 of Slowport.

66 OUTEN3_F_P APB_CLK single separate

It starts to assert the OE when the state machine 3 is

active for the mode 3 of Slowport.

67 PKDATA3_D_P APB_CLK single separate

It enters the read data packing state during the active

state machine 3 for the mode 3 of Slowport.

68 LADATA3_B_P APB_CLK single separate

It enters the data capturing cycle during the active

state machine 3 for the mode 3 of Slowport.

69 READY3_9_P APB_CLK single separate

It enters the acknowledge state to terminate the read

cycle when the state machine 3 is active for the mode

3 of Slowport.

Table 155. XPI PMU Event List (Sheet 3 of 4)