Hardware Reference Manual 281

Intel

®

IXP2800 Network Processor

Media and Switch Fabric Interface

The IXP2800 Network Processor supports all three methods. There are three groups of high-speed

pins to which this applies, as shown in Table 104, Table 105, and Table 106. The groups are

defined by the clock signal that is used.

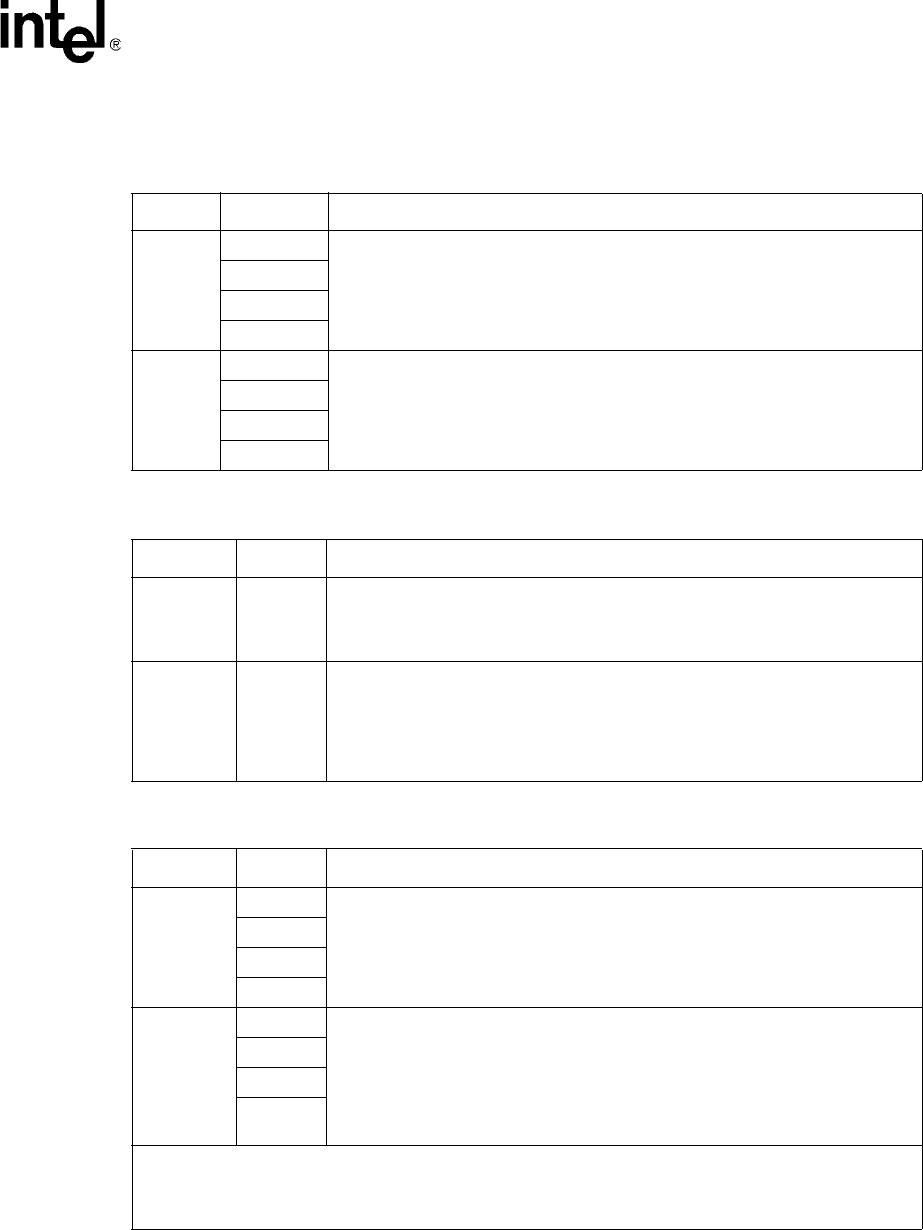

Table 104. Data Deskew Functions

Clock Signals IXP2800 Network Processor Operation

RCLK

RDAT 1. Sample point for each pin is programmed in Rx_Deskew.

2. Deskew values set automatically when training pattern (Section 8.6.1) is

received and is enabled in Train_Data[Ignore_Training].

RCTL

RPAR

RPROT

TCLK

TDAT 1. Send training pattern

• under software control (write to Train_Data[Continuous_Train] or

Train_Data[Single_Train])

• when TSTAT input has framing pattern for more than 32 cycles and enabled in

Train_Data[Train_Enable].

TCTL

TPAR

TPROT

Table 105. Calendar Deskew Functions

Clock Signals IXP2800 Network Processor Operation

RSCLK RSTAT

1. Used to indicate need for data training on receive pins by forcing to continual

framing pattern (write to Train_Data[RSTAT_En]).

2. Send training pattern under software control (write to

Train_Calendar[Continuous_Train] or Train_Calendar[Single_Train]).

TSCLK TSTAT

1. Sample point for each pin is set in Rx_Deskew, either by manual programming

or automatically.

2. Deskew values set automatically when training pattern (Section ) is received

and is enabled in Train_Calendar[Ignore_Training].

3. Received continuous framing pattern can be used to initiate data training

(Train_Data[Detect_No_Calendar]), and/or interrupt the Intel XScale

®

core.

Table 106. Flow Control Deskew Functions

Clock Signals IXP2800 Network Processor Operation

RXCCLK

RXCSOF 1. Sample point for each pin is programmed in Rx_Deskew.

2. Deskew values set automatically when training pattern (Section 8.6.2) is

received and is enabled in Train_Flow_Control[Ignore_Training].

Note 1, 2

RXCDAT

RXCPAR

RXCSRB

TXCCLK

TXCSOF 1. Send training pattern

• under software control (write to Train_Flow_Control[Continuous_Train] or

Train_Flow_Control[Single_Train])

• when TXCFC input has been asserted for more than 32 cycles and enabled in

Train_Flow_Control[Train_Enable].

Notes 1, 2

TXCDAT

TXCPAR

TXCSRB

NOTES:

1. TXCFC is not trained. RXCFC is driven out relative to RXCCLK; TXCFC is received relative to TXCCLK,

but is treated as asynchronous.

2. RXCFC can be forced asserted by write to Train_Flow_Control[RXCFC_En].