324 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

PCI Unit

9.2.2.1 Initialization by the Intel XScale

®

Core

The PCI unit is initialized to an inactive, disabled state until the Intel XScale

®

core has set the

Initialize Complete bit in the Control register. This bit is set after the Intel XScale

®

core has

initialized the various PCI base address and mask registers (which should occur within 1 ms of the

end of PCI_RESET). The mask registers are used to initialize the PCI base address registers to

values other than the default power-up values, which includes the base address visible to the PCI

host and the prefetchable bit in the base registers (see Table 120).

When the PCI unit is in the inactive state, it returns retry responses as the target of PCI

configuration cycles if the PCI Unit is not configured as the PCI host. In the case of PCI Unit being

configured as the PCI host, the PCI bus will be held in reset until the Intel XScale

®

core completes

the PCI Bus configurations and clears the PCI Reset (as described in Section 9.2.11).

Note: During PCI bus enumeration initiated by the Intel XScale

®

core, reading a non-existent address

(an address for which no target asserts DEVSEL) results in a Master Abort. The Master Abort then

results in an Intel XScale

®

Core Data Abort Exception that must be handled by the enumeration

software. When this occurs, the RMA bit in the PCI_CONTROL register and the RX_MA bit in

the PCI_CMD_STAT register is set. The enumeration software must then clear these bits before

continuing with the enumeration process.

9.2.2.2 Initialization by a PCI Host

In this mode, the PCI Unit is not hosting the PCI Bus regardless of the PCI_CFG[0] signal. The

host processor is allowed to configure the internal CSRs while the Intel XScale

®

core is held in

reset. The host processor configures the PCI address space, the memory controllers, and other

interfaces. Also, the program code for the Intel XScale

®

core may be downloaded into local

memory.

The host processor then clears the Intel XScale

®

core reset bit in the PCI Reset register. This de-

asserts the internal reset signal to the Intel XScale

®

core and the core begins its initialization

process. The PCI_SWIN and PCI_DWIN strap signals are used to select the window sizes to

SRAM BAR and DRAM BAR (see Table 121).

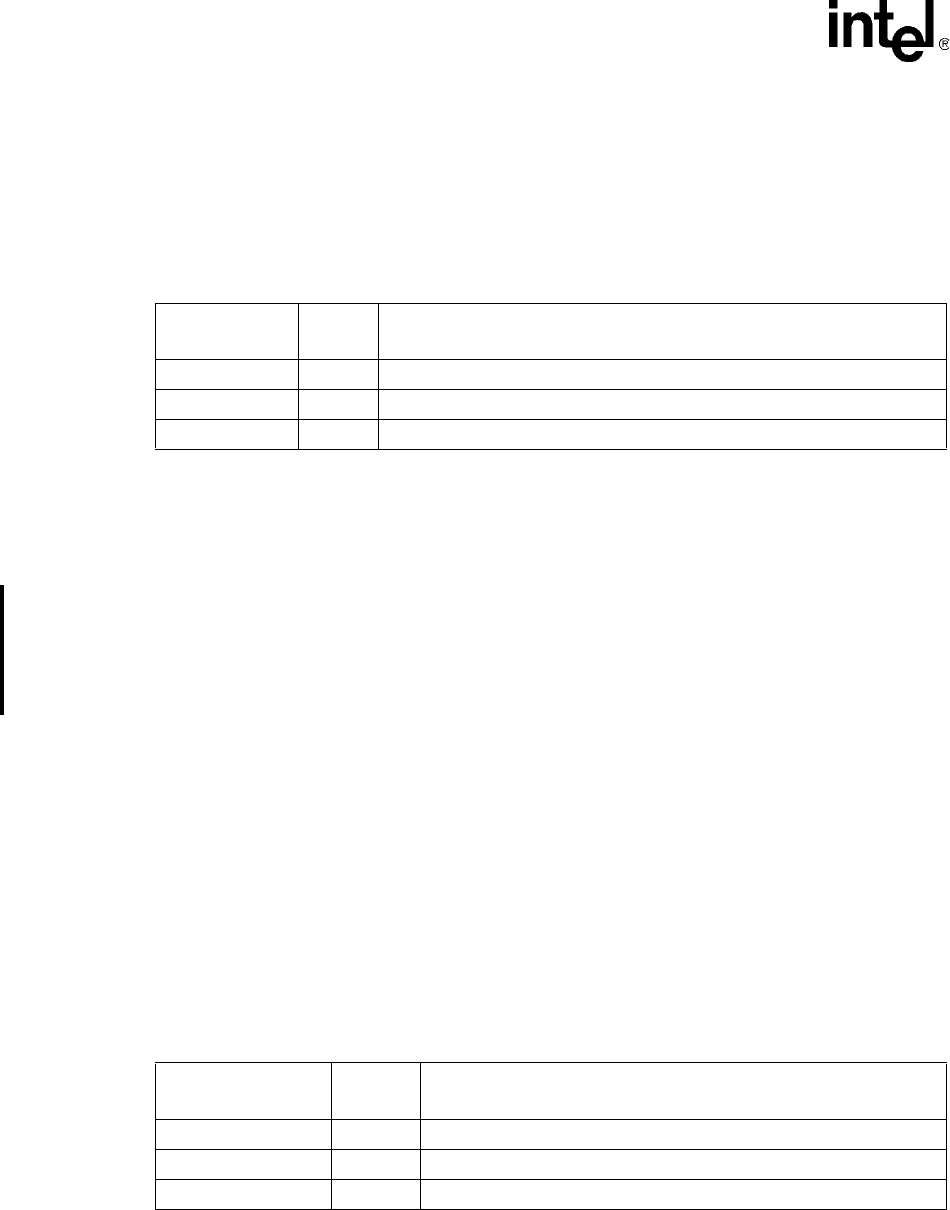

Table 120. PCI BAR Programmable Sizes

Base Address

Register

Address

Space

Sizes

PCI_CSR_BAR CSR 1 Mbyte

PCI_SRAM_BAR SRAM 0 Bytes; 128, 256, or 512 Kbytes; 1, 2, 4, 8, 16, 32, 64, 128, or 256 Mbytes

PCI_DRAM_BAR DRAM 0 Bytes; 1, 2, 4, 8, 16, 32, 64, 128, 256, or 512 Mbytes; 1 Gbyte

Table 121. PCI BAR Sizes with PCI Host Initialization

Base Address

Register

Address

Space

Sizes

PCI_CSR_BAR CSR 1 Mbyte

PCI_SRAM_BAR SRAM 32, 64, 128, or 256 Mbytes

PCI_DRAM_BAR DRAM 128, 256, or 512 Mbytes; 1 Gbyte