128 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

Intel XScale

®

Core

3.11.4 Atomic Operations

The Intel XScale

®

core has Swap (SWP) and Swap Byte (SWPB) instructions that generate an

atomic read-write pair to a single address. These instructions are supported for the SRAM and

Scratch space, and also to any other address space if it is done by a Read command followed by

Write command.

cbiIO is asserted when a data cache request is initiated to a memory region with cacheable and

bufferable bits in the translation table first-level descriptor set to 0. Also, if cbiIO is asserted during

the CMB read portion of the SWP, then it also does a Read Command followed by Write

Command, regardless of address. In those cases, the SWP/SWPB is atomic with respect to

processes running on the Intel XScale

®

core, but not with respect to the Microengines.

The following summarizes the Atomic operation.

When the Intel XScale

®

core presents the read command portion of the SWP, it will assert the

cbiLock signal. The gasket will “ack” the read and save the BufID in the push_ff. It will not

arbitrate for the command bus at that time; rather it will wait for the corresponding write of the

SWP (which will also have cbiLock asserted). At that time the gasket will arbitrate for the

command bus to send a command with the atomic operation in the command field (the command is

based on the address space chosen for the SRAM/Scratch, which has multiple aliased address

ranges).

The SRAM or Scratch controller will pull the data, do the atomic read-modify-write, and then push

the read data back. The gasket will use the saved BufID when returning the data to CMB.

Note: Unrelated reads, such as instruction and Page Table fetches, can come in the interval between the

read-lock and write-unlock, and will be handled by the gasket. No other data reads or writes will

come in that interval. Also, the Intel XScale

®

core will not wait for the SWP read data before

presenting the write data.

The gasket uses address aliases to generate the following atomic operations.

• Bit Set

• Bit Clear

• Add

• Subtract

• Swap

For the alias address type of atomic operation, the Intel XScale

®

core will issue a SWP command

with an alias address if it needs data return. The Intel XScale

®

core will use the write command

with an alias address if it does not need data return.

Xscale_IF will not check the second address, as long as it detects one write after one read, both

with cbiLock enabled. It will take the write

address and put it in the command.

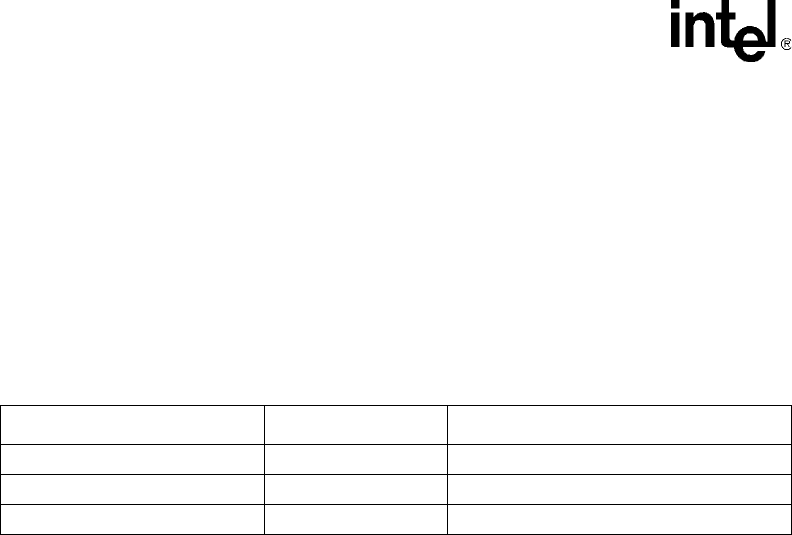

Address Space cbiIO Operation

SRAM/Scratch 0 RMW Command

Not SRAM/Scratch x Read Command followed by Write Command

Any 1 Read Command followed by Write Command