220 Hardware Reference Manual

Intel

®

IXP2800 Network Processor

SRAM Interface

6.7.2 Microcode Restrictions to Maintain Ordering

The microcode programmer must ensure order where the program flow requires order and where

the architecture does not guarantee that order. One mechanism that can be used to do this is

signaling. For example, if the microcode needs to update several locations in a table, a location in

SRAM can be used to lock access to the table. Example 31 is the microcode for this table update.

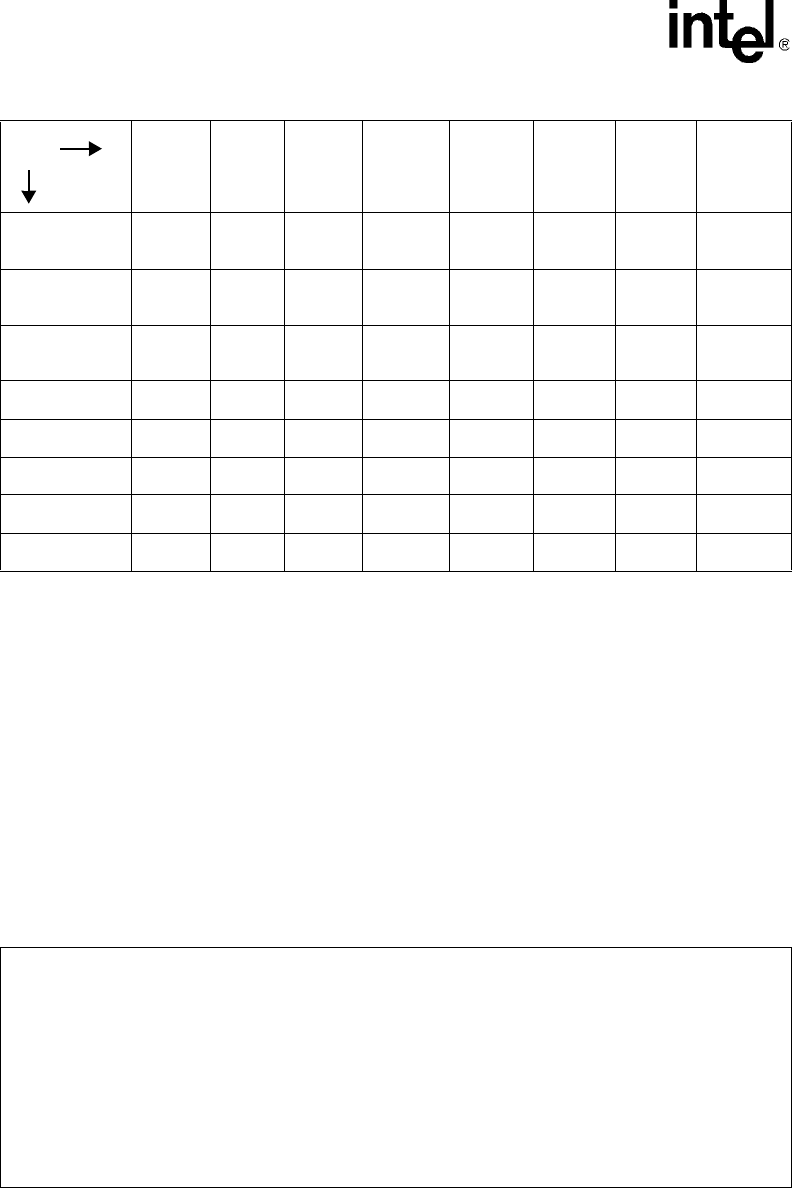

Table 78. Q_array Entry Reference Order

1

st

ref

2

nd

ref

Read_Q

_Descr

head,

tail

Read_

Q_Des

cr

other

Write_Q

_Descr

Enqueue Dequeue Put Get Journal

Read_Q_Descr

head,tail

Order

1

1. The order of Read_Q_Descr_head/tail after Write_Q_Descr to the same element will be guaranteed only if it is to a different

descriptor SRAM address. The order of Read_Q_Descr_head/tail after Write_Q_Descr to the same element with the same

descriptor SRAM address is not guaranteed and should be handled by the Microengine code.

Read_Q_

Descr other

Order

Write_Q_

Descr

2

2. Write_Q_Descr reference order is not guaranteed after any of the other references. The Queue array hardware assumes

that the Microengine managing the cached entries will flush an element ONLY when it becomes the LRU in the Microengine

CAM. Using this scheme, the time between the last use of this element and the write reference is sufficient to guarantee the

order.

Enqueue Order Order Order Order

3

3. Order between Enqueue references and Dequeue references are guaranteed only when the Queue is empty or near empty.

Dequeue Order Order Order

3

Order

Put Order

Get Order

Journal Order

Example 31. Table Update Microcode

IMMED [$xfer0, 1]

SRAM [write, $xfer0, flag_address, 0, 1, ctx_swap [SIG_DONE_2]

; At this point, the write to flag_address has passed the point of coherency. Do

the table updates.

SRAM [write, $xfer1, table_base, offset1, 2] , sig_done [SIG_DONE_3]

SRAM [write, $xfer3, table_base, offset2, 2] , sig_done [SIG_DONE_4]

CTX_ARB [SIG_DONE_3, SIG_DONE_4]

; At this point, the table writes have passed the point of coherency. Clear the

flag to allow access by other threads.

IMMED [$xfer0, 0]

SRAM [write, $xfer0, flag_address, 0, 1, ctx_swap [SIG_DONE_2]