Hardware Reference Manual 423

Intel

®

IXP2800 Network Processor

Performance Monitor Unit

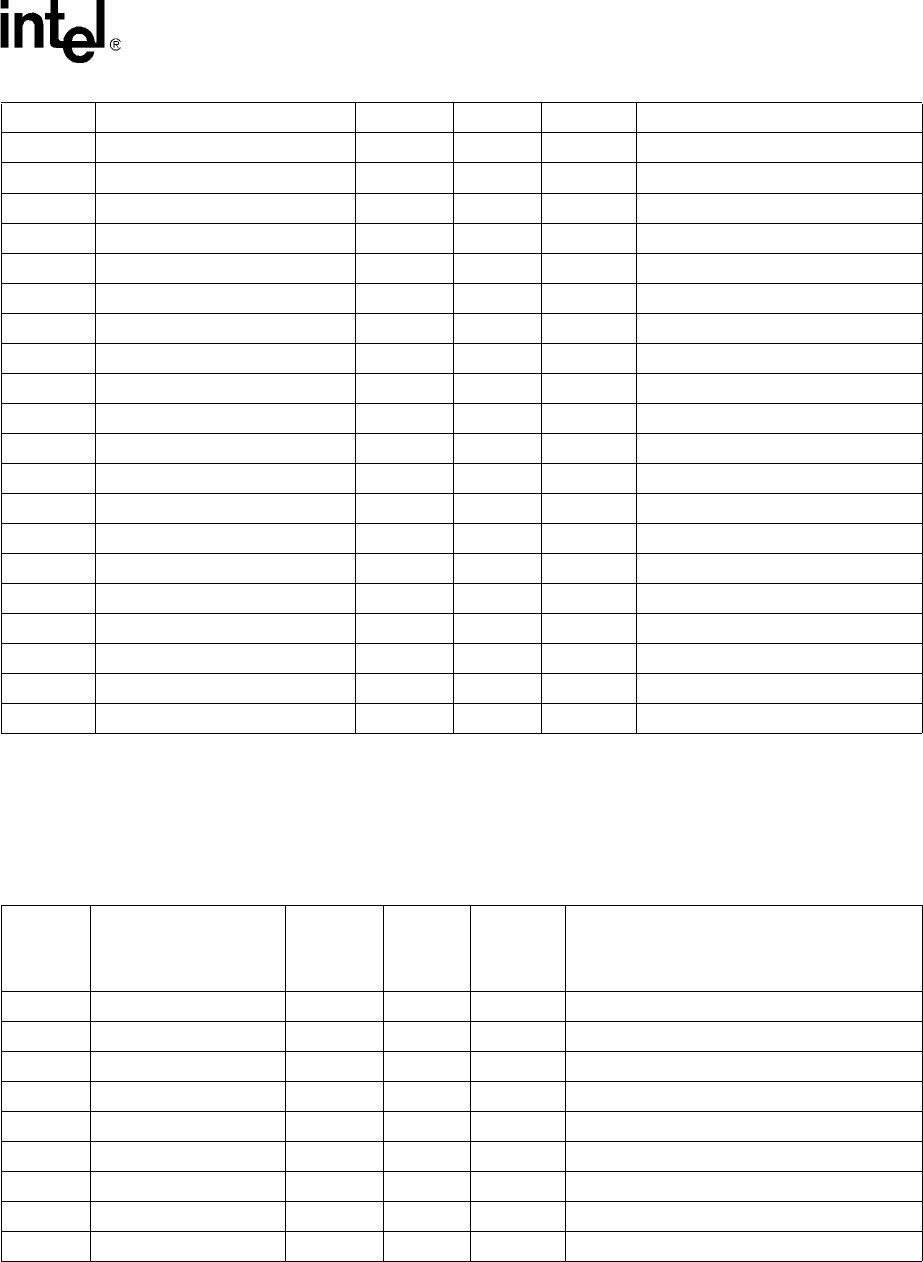

11.4.6.28 DRAM DPLA Events Target ID(010010) / Design Block #(0011)

33 FIFO Full – Queue Cmd Q P_CLK long separate FIFO Full – Queue Cmd Q

34 FIFO Dequeue – Rd Cmd Q S_CLK single separate FIFO Dequeue – Rd Cmd Q

35 FIFO Enqueue – Rd Cmd Q P_CLK single separate FIFO Enqueue – Rd Cmd Q

36 FIFO Valid – Rd Cmd Q S_CLK long separate FIFO Valid – Rd Cmd Q

37 FIFO Full – Rd Cmd Q P_CLK long separate FIFO Full – Rd Cmd Q

38 FIFO Dequeue – Oref Cmd Q S_CLK single separate FIFO Dequeue – Oref Cmd Q

39 FIFO Enqueue – Oref Cmd Q P_CLK single separate FIFO Enqueue – Oref Cmd Q

40 FIFO Valid – Oref Cmd Q S_CLK long separate FIFO Valid – Oref Cmd Q

41 FIFO Full – Oref Cmd Q P_CLK long separate FIFO Full – Oref Cmd Q

42 FIFO Dequeue – SP0 Pull Data Q S_CLK single separate FIFO Dequeue – SP0 Pull Data Q

43 FIFO Enqueue – SP0 Pull Data Q P_CLK single separate FIFO Enqueue – SP0 Pull Data Q

44 FIFO Valid – SP0 Pull Data Q S_CLK long separate FIFO Valid – SP0 Pull Data Q

45 FIFO Full – SP0 Pull Data Q P_CLK long separate FIFO Full – SP0 Pull Data Q

46 FIFO Dequeue – SP1 Pull Data Q S_CLK single separate FIFO Dequeue – SP1 Pull Data Q

47 FIFO Enqueue – SP1 Pull Data Q P_CLK single separate FIFO Enqueue – SP1 Pull Data Q

48 FIFO Valid – SP1 Pull Data Q S_CLK long separate FIFO Valid – SP1 Pull Data Q

49 FIFO Full – SP1 Pull Data Q P_CLK long separate FIFO Full – SP1 Pull Data Q

50 FIFO Dequeue – Push ID/Data Q P_CLK single separate FIFO Dequeue – Push ID/Data Q

51 FIFO Enqueue – Push ID/Data Q S_CLK single separate FIFO Enqueue – Push ID/Data Q

52 FIFO Valid – Push ID/Data Q P_CLK long separate FIFO Valid – Push ID/Data Q

53 FIFO Full – Push ID/Data Q S_CLK long separate FIFO Full – Push ID/Data Q

Table 181. SRAM CH0 PMU Event List (Sheet 2 of 2)

Table 182. IXP2800 Network Processor Dram DPLA PMU Event List (Sheet 1 of 2)

Event

Number

Event Name

Clock

Domain

Single

pulse/

Long

pulse

Burst Description

0 d0_enq_id_wph P_CLK single separate Enqueue d0 cmd

1 d0_deq_id_wph P_CLK single separate Dequeue d0 cmd

2 dram_req_rph[0] P_CLK single separate d0 has a valid req

3 next_d0_full_wph P_CLK single separate d0 FIFO hit the full threshold

4 d1_enq_id_wph P_CLK single separate Enqueue d1 cmd

5 d1_deq_id_wph P_CLK single separate Dequeue d1 cmd

6 dram_req_rph[1] P_CLK single separate d1 has a valid req

7 next_d1_full_wph P_CLK single separate d1 FIFO hit the full threshold

8 d2_enq_id_wph P_CLK single separate Enqueue d2 cmd